決勝AI晶片未來:CoWoS vs Foveros vs 混合鍵合封裝技術深度解析

本文深入剖析當前人工智慧 (AI) 晶片領域中三種領先的先進封裝解決方案:台積電的 CoWoS (Chip-on-Wafer-on-Substrate)、英特爾的 Foveros,以及廣泛定義下的混合鍵合 (Hybrid Bonding) 技術(包含台積電的 SoIC 和英特爾的 Foveros Direct 等具體實施方案);隨著 AI 技術的飛速發展,對運算能力和記憶體頻寬的需求呈指數級增長,傳統的晶片封裝技術已難以為繼,先進封裝技術因此扮演著至關重要的角色,不僅延續了半導體產業的發展趨勢,更成為提升 AI 晶片性能、降低功耗及實現異質整合的關鍵。

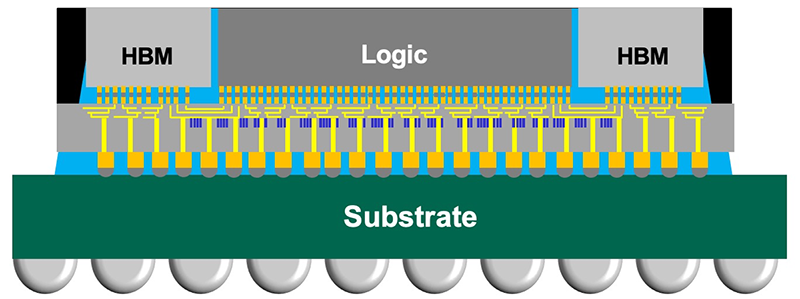

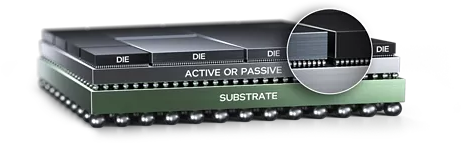

此圖為台積電 CoWoS-S 技術的結構示意圖,CoWoS-S 是一種 2.5D 先進封裝平台,專為人工智慧 (AI) 與超級電腦等高效能運算應用所設計,其核心是採用一片大型的矽中介層 (圖中灰色層),將邏輯晶片 (Logic) 與高頻寬記憶體 (HBM) 並排整合於其上,透過矽中介層上的高密度導線與矽穿孔 (TSV) 進行互連,實現了晶片間的超高頻寬通訊;此技術善用水平空間,將不同功能的小晶片緊密整合在單一基板上,是當前頂尖 AI 加速器廣泛採用的解決方案。 (圖片來源:TSMC)

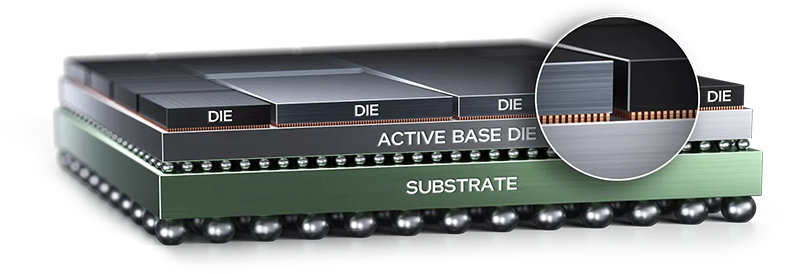

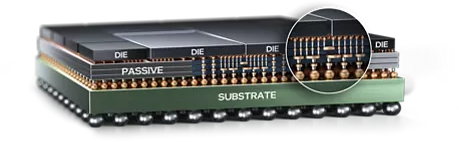

此圖為英特爾 Foveros 3D 封裝技術的渲染圖,Foveros 是一種真正的 3D 堆疊技術,它將多個小晶片 (Die) 垂直堆疊於一個作用中底層晶片 (Active Base Die) 之上,而非並排排列;其先進的 Foveros Direct 技術採用直接銅對銅 (Cu-to-Cu) 的混合鍵合方式(如放大圖所示),無需傳統的微凸塊,實現了更細微的互連間距與更高的整合密度;這種架構允許將來自不同製程甚至不同晶圓廠的小晶片靈活地整合在一起,創造出更緊湊、更強大的系統級晶片,是實現異質整合的關鍵技術。 (圖片來源:Intel)

當前先進封裝技術正沿著不同維度發展,以滿足 AI 晶片的需求;首先,台積電的 CoWoS 作為成熟的 2.5D 封裝典範,透過矽中介層將邏輯晶片與高頻寬記憶體 (HBM) 並排整合,有效提升了記憶體頻寬,廣泛應用於現今的高性能 AI 加速器。

接著,英特爾的 Foveros 技術將整合方式由平面推向了 3D 堆疊,其初期採用微凸塊 (micro-bumps) 實現晶片間的垂直互連,進一步縮短訊號路徑;而其技術藍圖的終極目標,則是名為 Foveros Direct 的混合鍵合 (Hybrid Bonding) 方案,混合鍵合是目前最前沿的 3D 封裝方式,它無需任何凸塊,直接以原子級的銅對銅 (Cu-to-Cu) 鍵合進行連接。這種革命性的方法帶來了前所未有的互連密度與極低的功耗。

本文將詳細比較這三種技術的核心原理、關鍵技術特性(包括互連密度、頻寬、功耗、散熱管理及可擴展性)、製造工藝成熟度、良率、成本考量、供應鏈生態,以及在現有 AI 晶片中的應用案例和未來發展藍圖;分析顯示,從 2.5D 的 CoWoS 到採用微凸塊的 3D Foveros,再到無凸塊的 3D 混合鍵合,不僅是漸進式的改良,更是應對 AI 晶片發展瓶頸、延續摩爾定律精神的典範轉移;這些技術各有其優勢與挑戰,並在 AI 硬體不斷演進的過程中扮演著不同但都至關重要的角色。

AI 加速對先進封裝的迫切需求

AI 硬體不斷演進的需求

現代 AI 模型,特別是大型語言模型 (LLM) 和生成式 AI,對運算能力和記憶體頻寬的需求正以前所未有的速度增長;AI 應用需要大量的平行運算能力和極高的記憶體頻寬來處理海量數據和複雜計算,傳統的單晶片系統 (SoC) 在尺寸、功耗和成本方面面臨越來越大的挑戰,難以滿足這些極端需求。

因此,異質整合 (Heterogeneous Integration) 成為 AI 硬體發展的必然趨勢,異質整合指的是將不同功能、不同製程節點製造的小晶片 (chiplets)——例如 CPU、GPU、專用 AI 加速單元、高頻寬記憶體 (HBM) 和 I/O 晶片——整合在單一封裝體中,這種方法允許每個小晶片採用最適合其功能的製程技術進行優化,從而提高整體系統的性能和成本效益。

封裝在系統性能和異質整合中的角色

先進封裝技術已超越其傳統的保護晶片、提供電氣連接的基礎功能,轉變為提升系統整體性能的關鍵因素,透過縮短晶片間的互連長度,先進封裝能夠顯著降低訊號延遲和功耗,同時增強訊號完整性。這對於需要高速數據傳輸和大量數據交換的 AI 應用至關重要。

「系統技術協同優化」(System-Technology Co-Optimization, STCO) 的概念日益受到重視,即封裝選擇與晶片架構設計緊密耦合、相互影響,封裝不再是晶片設計完成後的附加步驟,而是需要在設計初期就納入考量。

基於小晶片的設計方法正在改變晶片的架構方式,這種模組化方法在成本節約、可擴展性、和良率提升方面均優於傳統的單片晶片設計;CoWoS 技術明確支援小晶片架構,而 Foveros 和混合鍵合更是以支援小晶片整合為其核心理念。

隨著摩爾定律的物理極限日益臨近,以及新製程節點的開發成本急劇上升,先進封裝技術正成為晶圓代工廠和整合元件製造廠 (IDM) 之間競爭的主要戰場,提供卓越的封裝解決方案已成為關鍵的差異化優勢;小晶片架構的興起,正是借助先進封裝實現的,它允許設計者針對不同功能區塊選用最優的製程節點,從而繞過單一先進節點的成本和良率瓶頸,持續提升系統性能;台積電 (CoWoS, SoIC) 和英特爾 (Foveros, EMIB) 等行業巨頭均投入巨資,積極推廣其獨特的封裝技術組合;這種競爭態勢在產能擴張 和技術路線的直接比較中顯而易見,例如:英特爾宣稱其 Foveros 技術可以直接取代部分 CoWoS 設計,這預示著未來高性能半導體的領導地位,將同等依賴於封裝技術的先進性與製程技術的突破。

AI 的蓬勃發展也加速了先進封裝技術的普及化,推動這些原本主要應用於少數旗艦產品的高端技術,擴展到更廣泛的 AI 加速器市場;早期,如 CoWoS 這類的先進封裝主要用於頂級 GPU 和 FPGA;然而,AI 熱潮催生了來自不同參與者(包括開發自研晶片的雲端服務供應商)對 AI 加速器的巨大需求,這些參與者為了保持競爭力,迫切需要先進封裝帶來的性能優勢,需求的激增正驅動著封裝產能的擴張和產品線的多樣化,例如:CoWoS-L/R、Foveros 各版本以及多種混合鍵合方案的出現,這種更廣泛的應用,長遠來看將有助於降低這些高端封裝的成本(儘管仍屬高價位),並催生一個包含設計工具、IP 和專業技術的更大規模生態系統。

領先封裝技術深度剖析

台積電 CoWoS (Chip-on-Wafer-on-Substrate)

核心原理與衍生技術

CoWoS 是台積電推出的一種 2.5D 先進封裝技術,其核心思想是將邏輯晶片(如 GPU 或 AI 加速器)和高頻寬記憶體 (HBM) 等多個小晶片並排整合到一個中介層 (interposer) 上,然後再將帶有中介層的晶圓封裝到基板 (substrate) 上,這種結構有效地縮短了邏GIC晶片與 HBM 之間的距離,大幅提升了數據傳輸頻寬和效率。

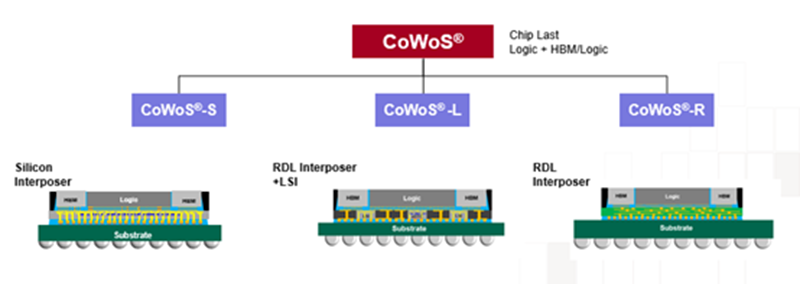

CoWoS 技術主要有以下幾種衍生型態:

CoWoS-S (Silicon Interposer):

採用矽中介層,並透過矽穿孔 (TSV) 技術實現晶片與中介層以及中介層與基板之間的高速電氣連接,矽中介層能夠提供極細的線路佈局,支援高密度互連,但隨著中介層尺寸的增大,其良率問題也日益凸顯。

CoWoS-R (Organic Interposer):

採用有機中介層,並在中介層上製作精細間距的重佈線層 (RDL) 來實現高速連接,有機中介層具有一定的撓性,可以作為應力緩衝層,有效緩解因中介層與基板之間熱膨脹係數 (CTE) 不匹配所引發的可靠性問題,因此在良率和可靠性方面相較於 CoWoS-S 更具優勢。

CoWoS-L (Local Silicon Interconnect):

這種技術結合了局部矽互連橋 (LSI) 和 RDL 有機中介層,形成所謂的重構中介層 (Reconstituted Interposer, RI),它採用晶片後置 (chip-last) 的組裝方式,目的在結合 CoWoS-S 的高密度 TSV 優勢與有機中介層的成本及良率效益,NVIDIA 的 Blackwell GPU 已宣布將採用 CoWoS-L 技術。

此圖展示了台積電 CoWoS (Chip-on-Wafer-on-Substrate) 先進封裝技術系列,這是一套專為滿足高效能運算 (HPC) 與 AI 應用而設計的異質整合平台,如圖所示,CoWoS 平台主要包含三種解決方案:採用大型「矽中介層」(Silicon Interposer) 的 CoWoS-S,可提供最高的互連密度;結合「局部矽互連橋」(LSI) 與 RDL 中介層的 CoWoS-L,在性能與成本上取得平衡;以及採用「RDL 中介層」的 CoWoS-R,提供具成本效益的彈性選擇。這一系列的技術組合讓客戶能依據產品需求,靈活整合邏輯晶片與高頻寬記憶體 (HBM),實現最佳的系統效能。(圖片來源:TSMC)

為了滿足 AI 晶片對更大整合面積和更多 HBM 堆疊的需求,台積電持續擴展 CoWoS 的能力,支援的中介層尺寸從現有的 3.5 倍光罩面積 (reticle size) 逐步擴展到 5 倍、9 倍甚至更大,目標是在 2027 年實現 9.5 倍光罩面積的 CoWoS 量產,能夠整合 12 個或更多 HBM 堆疊以及最先進的邏輯晶片。

關鍵技術屬性與性能指標

- 互連技術:主要依賴 TSV、微凸塊 (micro-bumps) 和 RDL 進行連接。

- 頻寬:透過將 HBM 與邏輯單元緊密放置,CoWoS 能夠實現極高的記憶體頻寬,例如,整合 4 顆 HBM2 即可達到 1TB/s 的頻寬,採用 CoWoS 技術的 UCIe IP 已展示出每毫米晶片邊緣 8 Tbps (Alphawave Semi) 甚至 10 Tbps (GUC, 32 Gbps/lane) 的頻寬密度。

- 功耗與散熱:CoWoS 透過在中介層內整合 RDL 供電/接地網路以及深溝槽電容 (DTC) 來增強電源完整性;同時,利用矽或有機中介層以及底部填充劑 (underfill) 材料來改善散熱管理。

AI 應用優勢

CoWoS 為 AI 工作負載帶來了顯著優勢,包括:為 GPU/AI 加速器和 HBM 提供高整合密度、降低延遲、實現高頻寬通訊,以及擁有成熟的生態系統支援。

AI 應用局限性

CoWoS 的主要局限性在於其製造複雜度高、成本昂貴,尤其對於 CoWoS-S 的大尺寸矽中介層而言,良率挑戰依然存在;此外,在高數據傳輸速率下,熱應力、電氣寄生效应等問題也需要仔細考量;更重要的是,CoWoS 的產能瓶頸,特別是在中介層供應方面,已成為限制 AI 晶片供應的關鍵因素。

主要 AI 晶片應用案例

眾多領先的 AI 晶片均採用 CoWoS 技術,例如:NVIDIA 的各代 GPU (包括 H100、Blackwell B 系列、A100);AMD 的 Instinct MI 系列加速器 (MI250, MI300);博通 (Broadcom) 的 AI ASIC;聯發科 (MediaTek) 的網路 ASIC;以及谷歌 (Google) 的 TPU 和其他 HPC/AI 加速器。

CoWoS 技術衍生型態(S、R、L)的演進,清晰地反映出台積電為應對不同市場區隔(特別是 AI 領域多樣化需求)而在性能、成本、良率和可擴展性之間不斷尋求平衡的努力;CoWoS-S 作為早期的高性能方案,在大尺寸矽中介層方面面臨良率和成本的挑戰;CoWoS-R 引入有機中介層,目的在改善可靠性和良率,並可能降低成本,但在超精細 RDL 間距方面可能不及矽中介層;CoWoS-L 則似乎是一種戰略性的折衷方案,它利用局部矽互連橋 (LSI) 在關鍵區域實現高密度連接,同時結合較大面積的 RDL 有機中介層,可能為如 NVIDIA Blackwell 這樣的大型封裝提供更優的成本-性能-可擴展性平衡;NVIDIA 等主要客戶轉向 CoWoS-L,突顯了其在下一代 AI 硬體中的重要性日益增加,這種產品線的多樣化使得台積電能夠滿足從超高性能到對成本更敏感的各種 AI 晶片設計需求,從而保持其市場領先地位。

CoWoS 的產能已成為 AI 硬體供應鏈中的關鍵瓶頸,直接影響著頂級 AI 加速器的市場供應,並對整體市場動態產生深遠影響;市場對 CoWoS 的需求(主要由 NVIDIA 驅動)持續超過供應能力,為此台積電正積極擴大產能,計劃到 2024 年將產能提升三倍以上,並在 2026 年前持續大幅增長,這種產能限制賦予了台積電相當大的定價權和決定客戶優先順序的影響力;同時,這也為競爭對手(如英特爾的 Foveros、三星的 I-Cube 以及其他 OSAT 廠商)提供了發展替代方案的機會;CoWoS 的瓶頸效應可能會決定 AI 硬體部署的速度,並可能影響 AI 晶片供應商的市場份額,因此對 CoWoS 產能的投資對於整個 AI 生態系統而言具有戰略意義。

英特爾 Foveros

核心原理

Foveros 是英特爾開發的一種 3D面對面 (face-to-face) 晶片堆疊封裝技術,初期版本採用微凸塊 (micro-bumps) 進行互連,其基本結構包含一個底部的基礎邏輯晶片 (base logic die),並在其上堆疊額外的功能小晶片,如其他邏輯晶片、記憶體、FPGA 或類比/射頻元件。

Foveros Omni

Foveros Omni 目的在解決早期 Foveros 技術在功率傳輸方面的限制,它允許頂部晶片懸垂於基礎晶片之外,使得可以從封裝基板向上構建銅柱,直接為頂部晶片供電,從而減少了因高電流通過 TSV 造成的訊號干擾,Foveros Omni 的目標凸塊間距為 25 微米。

Foveros Direct (混合鍵合)

Foveros Direct 是 Foveros 技術向混合鍵合的演進,採用直接銅對銅連接,消除了微凸塊,以實現更高的互連密度和更低的功耗;其目標互連間距小於 10 微米,並進一步縮小至小於 5 微米,此部分將在混合鍵合章節詳細介紹。

其他 Foveros 衍生技術 (Foveros-S, -R, -B)

Foveros-S:

採用矽中介層 (可達 4 倍光罩面積),適用於客戶端產品,支援多個頂部小晶片和主動式基礎晶片,自 2019 年起採用主動式基礎晶粒大規模生產。

Foveros-R:

採用 RDL 中介層,適用於客戶端和對成本敏感的市場區隔,支援複雜功能需求和多個頂部小晶片,預計 2027 年投產。

Foveros-B:

結合 RDL (用於電源和訊號) 與矽橋接器,為複雜設計提供靈活的解決方案,適用於客戶端和資料中心應用,支援多個基礎小晶片 (如快取記憶體分離、DVR 或 MIM),預計 2027 年投產。

關鍵技術屬性與性能指標

- 互連技術: 初期採用微凸塊 (第一代為 36µm 間距,828/mm²),早期版本透過 TSV 進行功率傳輸,Foveros Omni 目標為 25µm 間距,1600/mm²。

- 頻寬: 第一代 Foveros 的頻寬是同類 2.5D 矽中介層的 2-3 倍。

- 功耗效率: 第一代 Foveros 為 0.15 pJ/bit;Foveros Omni 低於 0.15 pJ/bit。

AI 應用優勢

相較於 2.5D 封裝,Foveros 提供了更高的邏輯密度、更低的寄生參數、更短的延遲以及更優的功耗效率,其整合來自不同製程節點或不同來源的小晶片的靈活性,對 AI 晶片設計尤為有利。

AI 應用局限性

3D 堆疊導致的熱密度增加是一大挑戰,早期版本中用於功率傳輸的 TSV 會引起干擾並佔用額外面積;此外,複雜性和成本也是考量因素。

主要 AI 晶片應用案例

英特爾的 Ponte Vecchio (資料中心 GPU Max 系列) 應用於 AI/HPC;英特爾的 Meteor Lake (Core Ultra 客戶端處理器) 整合了 AI Boost NPU;未來的 Xeon 處理器 Clearwater Forest 也將採用 Foveros 技術。

英特爾的 Foveros 技術路線圖(從標準版到 Omni、Direct,以及 S/R/B 等衍生版本)展示了一種戰略性的多管齊下方法,目的在涵蓋從客戶端到高性能資料中心 AI 的不同市場區隔,同時系統性地解決早期版本中存在的限制;最初的 Foveros(基於微凸塊)確立了 3D 堆疊能力,但也面臨功率傳輸和散熱方面的問題;Foveros Omni 的設計初衷便是解決功率 TSV 干擾問題,這對於高功率 AI 晶片至關重要;Foveros Direct 則代表了向混合鍵合的飛躍,以實現極致的密度和功效,這與行業發展趨勢相符。 Foveros-S(矽中介層)、-R(RDL 中介層)和 -B(RDL + 橋接器)的推出,表明英特爾正在針對不同的成本/性能/複雜性需求點定製解決方案,這與台積電 CoWoS 的多樣化策略相似;其中,Foveros-R 和 -B 明確計劃於 2027 年投產,這表明英特爾不僅在開發單一技術,更在構建一個適應性強的封裝平台,以支援其 IDM 2.0 戰略,並在包括關鍵的 AI 市場在內的各個應用層級與台積電競爭。

Foveros 的成功與英特爾更廣泛的晶圓代工雄心及其整合來自不同來源(甚至可能包括競爭對手晶圓廠)小晶片的能力緊密相連,這本身就是一個複雜的供應鏈和 IP 保護挑戰;Foveros 是英特爾晶圓代工服務 (IFS) 的基石,像 Meteor Lake 這樣的產品已經使用 Foveros 將英特爾自家晶圓廠生產的晶片與台積電生產的晶片整合在一起,英特爾也明確表示 Foveros 可以整合來自不同晶圓廠的晶片;這在已知良好裸晶 (KGD) 採購、測試以及管理不同製造合作夥伴之間的知識產權方面帶來了挑戰;英特爾宣稱能夠將 CoWoS 設計「無需任何設計更改」地移植到 Foveros,這是一個吸引台積電客戶的大膽聲明,但對於涉及來自不同來源的多個小晶片的複雜 AI 晶片而言,此類移植的實際操作仍然是一項重大工程;如果英特爾能夠成功地大規模且經濟高效地管理這種多源整合,它可能會透過為 AI 晶片封裝提供一個可靠的大批量替代方案來顯著改變晶圓代工格局,從而挑戰台積電 CoWoS 生態系統的地位;然而,業界對於客戶是否會常態性地從一家晶圓廠購買晶圓然後在另一家進行封裝仍存有疑慮。

混合鍵合 (Hybrid Bonding):下一代前沿技術

核心原理

混合鍵合是一種先進的晶片互連技術,其核心在於實現直接的銅對銅 (Cu-Cu) 以及介電質對介電質 (dielectric-to-dielectric) 的鍵合,從而完全消除了傳統封裝中使用的焊料凸塊 (solder bumps) 或微凸塊 (micro-bumps),這種「無凸塊」(bumpless) 的連接方式使得晶片可以更緊密地堆疊,並達到極細的互連間距。

主要實施方案

- 台積電 SoIC (System-on-Integrated-Chips):SoIC 是台積電的混合鍵合解決方案,能夠實現不同尺寸、功能和製程節點的已知良好裸晶 (KGD) 的高密度垂直堆疊;其鍵合間距從次 10 微米開始,並持續微縮,透過 SoIC 整合的晶片系統可以進一步整合到 CoWoS 或 InFO 等封裝平台中,形成更複雜的系統級封裝;AMD 的 3D V-Cache 技術即採用了 SoIC-X。

- 英特爾 Foveros Direct:這是英特爾在其 Foveros 產品線中導入的混合鍵合技術,專為 3D 堆疊而設計,其目標是實現小於 10 微米,進而小於 5 微米,最終達到 3 微米的銅對銅鍵合間距。

- 三星 X-Cube (HCB - Hybrid Copper Bonding variant):三星的 X-Cube 是其佈局 3D IC 封裝的關鍵解決方案,其技術藍圖依序涵蓋了兩種不同的互連方式;首先,其早期方案採用「微凸塊」(micro-bumps) 進行晶片堆疊,三星先前規劃此版本於 2024 年準備就緒並投入量產;更進一步,三星正積極發展其下一代技術——無凸塊的「混合銅鍵合」(Hybrid Copper Bonding, HCB) 版本,此方案採用直接銅對銅鍵合,目標是在 2026 年實現量產,以應對未來 AI 晶片對極致互連密度的需求。

關鍵技術屬性與前所未有的互連密度

- 互連間距: 混合鍵合技術能夠將互連間距從 10 微米以下推進到亞微米級別,甚至奈米級,例如,imec 已展示了 400 奈米的間距;台積電 SoIC 的起始間距在次 10 微米;英特爾 Foveros Direct 的目標是小於 5 微米,然後是 3 微米;三星的 X-Cube HCB 也將採用無凸塊設計。

- 優勢: 更低的電阻、每位元更低的功耗、更短的延遲以及數量級提升的連接密度。

AI 應用優勢

混合鍵合為 AI 工作負載帶來了革命性的潛力,它能夠實現記憶體與邏輯單元之間,或邏輯單元之間的極高 I/O 密度堆疊,從而顯著提升頻寬和功耗效率,這對於克服 AI 領域長期存在的「記憶體牆」瓶頸至關重要;此外,混合鍵合還有助於實現更薄的封裝體,並在某些方面改善散熱性能。

AI 應用局限性

混合鍵合技術的製造極具挑戰性,需要極其平坦的晶圓表面(透過化學機械研磨 CMP 實現)、嚴格的污染控制以及高精度的對準技術;與成熟的凸塊鍵合方法相比,其初期成本更高,良率也面臨更大挑戰;儘管散熱有所改善,但在高密度堆疊結構中,熱管理依然是一個需要仔細應對的問題。

新興 AI 晶片應用與潛力

混合鍵合技術已開始應用於高頻寬記憶體 (HBM) 的多層堆疊 (如 16-Hi 及更高層數);AMD 的 3D V-Cache 技術(將 SRAM 堆疊在邏輯晶片上)是其早期成功應用之一;未來,NVIDIA 的 Rubin AI 架構和蘋果的 M5 SoC 預計將採用台積電的 SoIC 技術;英特爾的 Clearwater Forest 處理器也將使用 Foveros Direct;博通和 Marvell 也在積極探索混合鍵合的應用;AI 加速器和資料中心 XPU 是混合鍵合的重要目標市場。

混合鍵合不僅僅是一項漸進式的改進,更是一項根本性的技術轉變,它重新定義了晶片間互連的界限,並將關鍵的封裝步驟轉移到了前端晶圓廠的製程環境中;傳統的封裝技術,即使是像 CoWoS 或 Foveros 這樣採用微凸塊的先進封裝,其連接方式仍依賴於凸塊和焊料,這些技術在間距微縮方面面臨著約 10-20 微米的物理極限;混合鍵合則完全摒棄了凸塊和焊料,透過直接的銅對銅連接,將互連間距推向了 10 微米以下乃至亞微米級別,實現這種超精細連接的前提是需要前端晶圓廠級別的製程能力,例如:用於實現極致表面平坦度的化學機械研磨 (CMP) 和嚴格的潔淨度控制,這種轉變對傳統的委外封裝測試廠 (OSAT) 構成了重大影響,它們必須進行調整,否則可能在這一關鍵製程環節被邊緣化;這種封裝製程的「前端化」模糊了晶圓製造與封裝之間的界線,要求更緊密的協同設計與合作,並可能使更多價值集中在擁有這些前端製程能力的大型晶圓代工廠和 IDM 廠商手中。

儘管混合鍵合技術潛力巨大,但其在複雜 AI 晶片中的廣泛應用,將取決於能否實現大規模量產的成熟度、可接受的良率以及成本效益,特別是對於異質整合至關重要的晶片對晶圓 (Die-to-Wafer, D2W) 製程;晶圓對晶圓 (Wafer-to-Wafer, W2W) 的混合鍵合技術相對成熟,已應用於影像感測器和 3D NAND 等領域;然而,W2W 製程在實施已知良好裸晶 (KGD) 策略方面存在困難,而 KGD 對於複雜且昂貴的 AI 小晶片而言至關重要;D2W 製程對於異質整合不同尺寸和類型的小晶片至關重要,但其成熟度較低,且面臨著晶片處理過程中的顆粒污染控制以及產能較低等挑戰。CMP、潔淨度和對準等方面的嚴格要求,使得該製程本質上成本高昂且複雜,直接影響良率,各大廠商正投入巨資以克服這些挑戰,例如:台積電的 SoIC、英特爾的 Foveros Direct 以及三星的 X-Cube HCB 都在積極擴產並發布了相關路線圖;D2W 混合鍵合技術的成熟速度,將直接影響基於小晶片的 AI 架構潛力能否充分釋放,D2W 在成本和良率方面的突破,可能會極大地加速 AI 硬體的創新步伐。

AI 晶片封裝方案比較分析:CoWoS vs. Foveros vs. 混合鍵合

本節將基於第三節的詳細屬性,對 CoWoS、Foveros 及混合鍵合技術進行直接的、逐項的特性比較。

互連密度與頻寬能力

- CoWoS:依賴於中介層上的 TSV 和微凸塊,其密度受限於中介層佈線能力和凸塊間距(C4 凸塊通常大於 40-50µm,連接 HBM 的微凸塊則更精細);CoWoS-L 的 RDL 提供了精細間距的連接,基於 CoWoS 的 UCIe 介面已展示出每毫米晶片邊緣 8-10 Tbps 的頻寬。

- Foveros (微凸塊):第一代產品的凸塊間距為 36µm (密度 828/mm²),Foveros Omni 則目標為 25µm (密度 1600/mm²),其頻寬約為 2.5D 矽中介層的 2-3 倍。

- 混合鍵合 (Foveros Direct, SoIC, X-Cube HCB):能夠實現小於 10µm 甚至亞微米級的互連間距(例如:台積電 SoIC 的 9µm,英特爾 Foveros Direct 的小於 5µm,imec 的 400nm 成果);Foveros Direct (<10µm 間距) 的密度可超過 10,000/mm²;混合鍵合提供了最高的 I/O 數量和擴展的頻寬。

混合鍵合技術在互連密度方面實現了質的飛躍,其提供的頻寬能力遠超基於微凸塊的解決方案,從根本上改變了晶片間通訊的可能性,對 AI 發展尤為關鍵,微凸塊的間距(無論是 CoWoS 還是 Foveros)均在數十微米的量級;相比之下,混合鍵合則將間距縮小至 10 微米以下,甚至亞微米級別。由於互連密度與間距的平方成反比,間距縮小 10 倍即可帶來 100 倍的密度提升,這種並行連接數量的大幅增加,直接轉化為更高的總頻寬,並允許更細粒度的邏輯與記憶體劃分,這不僅僅代表著更多的數據通道,更重要的是,它使得記憶體能夠真正普及化並與運算單元緊密耦合,這對 AI 性能而言是夢寐以求的目標。

表 1:先進封裝技術互連規格比較

|

技術解決方案 |

主要互連方式 |

最小互連間距 (µm) |

典型互連密度 (連接數/mm²) |

最大報告頻寬 (Tbps/mm 晶片邊緣) |

典型功耗效率 (pJ/bit) |

|

CoWoS-S |

矽中介層 + 微凸塊 |

>10 (微凸塊) |

數百至數千 (取決於凸塊) |

~1-2 (HBM 接口) |

較高 |

|

CoWoS-L (UCIe) |

RDL 有機中介層 + LSI + 微凸塊 |

>10 (微凸塊) |

數百至數千 (取決於凸塊) |

8-10 |

中等 |

|

Foveros Gen1 |

主動基礎晶片 + 微凸塊 |

36 |

828 |

N/A |

0.15 |

|

Foveros Omni |

主動基礎晶片 + 微凸塊 (外部供電) |

25 |

1600 |

N/A |

<0.15 |

|

Foveros Direct (<10µm) |

直接 Cu-Cu 混合鍵合 |

<10 |

>10,000 |

N/A |

<0.05 |

|

Foveros Direct (<5µm) |

直接 Cu-Cu 混合鍵合 |

<5 |

>40,000 (估算) |

N/A |

更低 (預期) |

|

TSMC SoIC (通用) |

直接 Cu-Cu 混合鍵合 |

<10 至 ~1 |

極高 |

N/A |

低 |

|

Samsung X-Cube HCB |

直接 Cu-Cu 混合鍵合 |

<10 (預期) |

極高 (預期) |

N/A |

低 (預期) |

註:N/A 表示相關數據未在參考資料中明確提供或不適用於該比較維度,頻寬和功耗效率會因具體設計和應用而有很大差異。

功率傳輸與效率

- CoWoS:採用 RDL 進行供電/接地網路佈局,並整合 DTC 以提升電源完整性,但在高數據切換率下仍面臨電源完整性挑戰。

- Foveros (微凸塊):早期版本中的功率 TSV 易引發干擾,Foveros Omni 透過外部供電銅柱解決了此問題,其功耗效率分別為:第一代 0.15 pJ/bit,Omni 低於 0.15 pJ/bit。

- 混合鍵合 (Foveros Direct, SoIC, X-Cube HCB):直接的銅對銅連接具有更低的電阻,從而降低每位元傳輸功耗;Foveros Direct 的目標是低於 0.05 pJ/bit;英特爾的 PowerVia(背面供電)技術與 Foveros Direct 相輔相成,進一步提升了功耗效率。

混合鍵合技術,特別是與背面供電等創新技術結合時,為實現超低功耗互連提供了最具前景的途徑,這對於管理未來 AI 系統巨大的功耗預算至關重要;互連功耗是電阻、電容和數據速率的函數,與直接銅連接相比,焊料凸塊甚至微凸塊都具有更高的電阻;混合鍵合的直接銅對銅路徑最大限度地降低了電阻。同時,3D 堆疊帶來的更短互連長度也降低了電容;英特爾的 Foveros Direct 明確將功耗目標定在 <0.05 pJ/bit,顯著低於其基於微凸塊的前代產品;背面供電技術(如英特爾的 PowerVia )將電源和訊號佈線分離,進一步優化了兩者並減少了電壓降,這與高密度的 3D 混合鍵合堆疊是相輔相成的;隨著 AI 模型的規模持續擴大,數據傳輸所消耗的功率成為主導因素,混合鍵合卓越的每位元功耗效率對於 AI 性能的可持續擴展至關重要。

散熱管理策略與挑戰

- CoWoS:矽或有機中介層以及底部填充劑有助於管理 CTE 不匹配問題和散熱;然而,CTE 不匹配仍然是一個挑戰。

- Foveros (微凸塊):3D 堆疊中增加的功率密度是主要的散熱考量;頂部晶片可能會阻礙散熱路徑,英特爾的 ODI (Omni-Directional Interconnect) 技術曾被提出用於改善散熱,允許堆疊晶片直接接觸散熱器。

- 混合鍵合:在某些情況下,消除底部填充劑和凸塊可以降低熱阻;然而,極高密度的 3D 堆疊仍然會集中熱量。先進的散熱解決方案(如微流控、先進熱介面材料 TIMs)至關重要。

- 通用 3D IC 散熱挑戰:每單位面積功率增加、非均勻功率分佈圖、3D 熱串擾等。

儘管 3D 堆疊(Foveros、混合鍵合)提供了密度和性能優勢,但它加劇了散熱挑戰;CoWoS (2.5D) 在將熱量分佈到較大中介層面積方面具有固有優勢,有效的熱協同設計和先進的散熱創新對於 3D 堆疊的 AI 晶片至關重要;垂直堆疊主動晶片(Foveros、混合鍵合)會使熱源集中,從上層晶片到散熱器的散熱路徑被拉長,並且可能受到下層晶片和介面材料的阻礙;作為 2.5D 技術的 CoWoS 允許晶片在中介層上分散佈局,從而為每個晶片提供了更好的接觸封裝基板和散熱器的途徑;雖然混合鍵合可以透過消除底部填充劑來降低一些介面熱阻,但整體熱密度仍然是主要問題,諸如英特爾 ODI 或先進散熱技術(液冷、微流控)等解決方案對於高功率 3D AI 晶片變得不可或缺,因此,散熱管理,而不僅僅是互連技術,將成為決定高功率 AI 加速器 3D 堆疊實用極限的關鍵因素;如果散熱問題得不到充分解決,「熱牆」可能會限制性能的提升。

可擴展性:晶片尺寸、堆疊層數與未來潛力

- CoWoS:支援大尺寸中介層(台積電路線圖顯示到 2027 年可達 9.5 倍光罩尺寸 )和多個 HBM 堆疊(4 個以上,CoWoS-L 可達 12 個 ),台積電的 SoW-X (基於 CoWoS) 目標是到 2027 年實現當前 CoWoS 運算能力的 40 倍。

- Foveros:基礎晶片最大可達 600mm²,多個基礎晶片可以透過 co-EMIB 技術拼接;Foveros Omni 消除了頂部晶片相對於基礎晶片的尺寸限制。

- 混合鍵合:能夠堆疊更多層數(例如 HBM 超過 16-Hi ),是 3D SoC、記憶體堆疊邏輯、邏輯堆疊邏輯的關鍵技術,其間距微縮路線圖已達數百奈米級別,imec 已展示 400nm 間距。

混合鍵合為垂直整合(堆疊層數和互連密度)提供了最具潛力的擴展路徑,而 CoWoS 在橫向擴展(中介層尺寸)方面處於領先地位;Foveros 則重點在尋求平衡,利用 EMIB 實現 3D 堆疊模組的橫向擴展。CoWoS 透過增加中介層尺寸來實現擴展,允許更多的小晶片和 HBM 並排佈置,這本質上是封裝級別的水平擴展;Foveros 透過堆疊晶片進行垂直擴展,其超大型系統的橫向擴展則依賴於將 Foveros 模組與 EMIB(2.5D 橋接技術)相結合。混合鍵合的主要優勢在於超精細間距的垂直互連,能夠實現更多的堆疊層數和更密集的層間連接,這使得混合鍵合成為實現真正 3D SoC(功能區塊垂直劃分)的理想選擇;未來可能會出現組合方案:利用混合鍵合實現密集的垂直堆疊(例如邏輯-記憶體),然後再利用 CoWoS 中介層或 EMIB 等技術將這些 3D 堆疊整合到更大的系統中,這種分層的擴展方法能夠應對不同層面的系統複雜性。

製造工藝成熟度、生產良率與成本影響

- CoWoS:是一項成熟技術(自 2011 年開始出貨 ),但其複雜性導致成本較高,且面臨良率挑戰,特別是對於大尺寸矽中介層 (CoWoS-S);CoWoS-R/L 重點在改善良率和成本。

- Foveros (微凸塊):自 2019 年開始量產,其位於新墨西哥州的大批量生產工廠 Fab 9 已投入運營;Fab 9 的建造成本 (35 億美元) 表明了其高昂的投資,對於多小晶片整合而言,良率是一個關鍵因素,需要複雜的驗證流程。

- 混合鍵合:W2W 混合鍵合在影像感測器/NAND 領域已較為成熟,而對於異質整合 AI 晶片至關重要的 D2W 混合鍵合,其成熟度較低,面臨著顯著的良率挑戰(如顆粒污染、對準精度、表面平坦度)和更高的成本。該技術需要前端晶圓廠的製程能力。

CoWoS 是目前用於大規模 AI 異質整合最成熟的技術,但成本較高,Foveros(微凸塊)在產量上正在追趕;混合鍵合雖然具有最高的性能潛力,但在複雜邏輯/AI D2W 應用方面成熟度最低,目前成本和良率風險也最高;CoWoS 擁有十多年的生產歷史,其成本和良率相對可控,儘管對於最大、最複雜的 AI 設計而言仍具挑戰性;Foveros(微凸塊)已量產數年,英特爾正在擴大其產能,其成本結構與英特爾的整合製造模式相關;混合鍵合的 D2W 流程對於 AI 小晶片至關重要,但其過程複雜,涉及 KGD 測試、等離子活化、精密對準和極高的潔淨度等步驟,這些都導致了更高的成本和良率敏感性。將混合鍵合製程轉移到晶圓廠,雖然利用了現有的專業知識,但也代表著這些步驟將與晶圓廠資源競爭,並帶有前端製程的成本特性;顯然存在一個權衡:最高的潛在性能(混合鍵合)伴隨著目前最高的成本/風險;CoWoS 提供了一條經過驗證但昂貴的途徑,Foveros 則重點在提供一個具有競爭力的替代方案,AI 晶片設計者必須根據其特定的產品需求和產量預期來權衡這些因素。

表 2:先進封裝技術製造與成本概況比較

|

技術解決方案 |

當前製造工藝成熟度 |

主要良率挑戰 |

相對製造成本 (相較於傳統封裝) |

主要供應鏈參與者/依賴性 (晶圓廠, OSAT, 設備, 材料) |

|

CoWoS (通用) |

高批量生產 |

大尺寸中介層 (尤其 Si)、TSV、多晶片整合 |

高 |

TSMC 主導;部分 OSAT (ASE, Amkor);中介層供應 |

|

Foveros (微凸塊) |

高批量生產 |

多小晶片 KGD、堆疊對準、散熱 |

高 (取決於複雜度) |

Intel 主導 (Fab 9);IFS 目標外部客戶 |

|

混合鍵合 (D2W 邏輯/AI) |

有限生產/開發中 |

顆粒控制、表面平坦度 (CMP)、對準精度 |

極高 |

晶圓廠 (TSMC, Intel, Samsung) 主導;專業設備商 |

供應鏈生態系統與產能現狀

- CoWoS:市場由台積電主導,目前正在進行大規模產能擴張;部分 OSAT 廠商(如日月光、艾克爾)提供類似 CoWoS 的服務或與台積電合作,中介層的供應可能成為瓶頸。

- Foveros:主要依賴英特爾內部產能(如位於新墨西哥州的 Fab 9);英特爾晶圓代工服務 (IFS) 重點在向外部客戶提供 Foveros 技術;英特爾計劃將 Foveros 產量提高 30%,EMIB-T 產能提高 150%。

- 混合鍵合:由於其對前端製程的要求,晶圓代工廠/IDM(如台積電的 SoIC、英特爾的 Foveros Direct、三星的 X-Cube HCB)在開發中處於領先地位;設備供應商(如 BESI、EVG、應用材料、東京威力科創、ASMPT 等)扮演著關鍵角色;OSAT 廠商正在調整其工作流程,但面臨較高的進入門檻。

目前,台積電在 AI 高端先進封裝領域(主要是 CoWoS)擁有最大且最成熟的生態系統,英特爾正迅速建設其 Foveros 產能和生態系統以展開競爭;混合鍵合的供應鏈仍在成熟過程中,由於技術的前端特性,晶圓代工廠處於主導地位,台積電的 CoWoS 是目前大批量 AI 封裝的領先者,擁有穩固的客戶基礎(NVIDIA、AMD 等)和持續的巨額產能投資;英特爾的 Foveros 是其自身產品戰略和晶圓代工雄心的核心,Fab 9 的啟用和計劃中的產能提升是這一戰略的關鍵;混合鍵合需要專業設備和超潔淨環境,使得晶圓廠成為當然的早期採用者和產能持有者,關鍵的設備和材料供應商在推動這一技術發展中扮演著至關重要的角色。OSAT 廠商在混合鍵合領域面臨更高的進入門檻,因為需要大量的資本投入和嚴格的製程控制,它們的角色可能會更多地轉向混合鍵合在晶圓廠完成後的最終組裝和測試,最先進封裝的供應鏈正日益集中於主要的晶圓代工廠/IDM,這可能導致對少數幾家廠商在尖端 AI 晶片製造方面的依賴性增加,但同時也促進了製程與封裝之間深度的協同開發。

共生關係:這些技術如何演進與互補

混合鍵合作為 Foveros 的演進/增強 (Foveros Direct)

Foveros Direct 是英特爾明確的混合鍵合實施方案,它是從基於微凸塊的 Foveros 技術演進而來,其目標是提供遠比微凸塊更精細的互連間距(從 <10µm 到 <5µm),並採用無凸塊的銅對銅直接連接,從而實現比其前代微凸塊技術更高的密度和更低的功耗,這使得 Foveros 技術能夠擴展到更高的互連密度,以滿足未來 AI 晶片的嚴苛需求。

SoIC 作為 CoWoS 的補充,實現先進系統整合

台積電的 SoIC(混合鍵合)技術能夠實現小晶片 (KGD) 的超高密度垂直堆疊,這些透過 SoIC 整合的「晶片系統」可以作為一個組件,進一步整合到更大的 CoWoS 封裝中;CoWoS 封裝還可以在共享的中介層上承載 HBM 和其他組件,這形成了一種分層的系統整合方式:SoIC 負責晶片級的 3D 整合,而 CoWoS 則負責封裝級的 2.5D/系統整合;AMD 的 MI300 系列產品就是一個例證,它首先使用 SoIC 進行 CPU 和 GPU 晶片的整合,然後再透過 CoWoS 技術與 HBM 進行封裝。

異質整合與小晶片的趨勢

CoWoS、Foveros 和混合鍵合這三大技術系列都是異質整合的關鍵推動者,它們使得晶片設計者能夠將來自不同製程節點甚至不同晶圓代工廠的小晶片混合搭配,這種模組化對於優化複雜 AI 系統的性能、功耗和成本 (PPAC) 至關重要,混合鍵合技術憑藉其極其精細的間距,允許更細粒度的小晶片劃分和更緊密的耦合。

2.5D 和 3D 封裝之間的界線正在變得模糊,混合方法(如 SoIC-on-CoWoS 或 Foveros Direct-on-EMIB)正變得普遍,以實現最佳的系統級性能,這標誌著向「系統級封裝」的轉變,其中封裝本身就是一個複雜的整合系統;CoWoS 本質上是 2.5D(晶片在中介層上),Foveros 是 3D(堆疊晶片),而混合鍵合是一種 3D 互連技術;然而,台積電將 SoIC(3D 混合鍵合堆疊)定位為可以整合到 CoWoS(2.5D 平台)中的技術,AMD MI300 即採用了此方案;英特爾則將 Foveros Direct(3D 混合鍵合堆疊)與 EMIB(2.5D 橋接技術)相結合,創建了「EMIB 3.5D」系統;這表明設計者並非在這些技術中擇一,而是將它們作為構建更複雜、多層次封裝結構的基礎模塊,封裝設計正變得與晶片設計一樣複雜,需要新的工具、方法論以及在晶片、封裝和系統協同設計方面的專業知識。封裝不再是事後的考慮,而是關鍵的架構組件。

混合鍵合技術作為一種「通用連接器」技術,既可以增強現有的基於 2.5D 中介層的架構(透過實現更密集的小晶片到中介層或中介層上小晶片之間的連接),也可以改進純粹的 3D 堆疊方法;其直接銅對銅的核心特性使其具有廣泛的適用性,混合鍵合的核心是直接的金屬對金屬和介電質對介電質的鍵合,這可以應用於晶圓對晶圓 (W2W)、晶片對晶圓 (D2W) 或晶片對晶片 (D2D) 的鍵合方式;在 Foveros Direct 中,它用於在主動基礎晶片上進行 D2W 或 D2D 堆疊;在台積電的 SoIC 中,它用於 D2W 或 W2W 以創建 3D 堆疊小晶片,雖然 CoWoS 傳統上使用微凸塊將晶片連接到中介層,但未來的發展可能會看到混合鍵合被用於實現放置在 CoWoS 型中介層上的小晶片之間,或直接在主動中介層上使用混合鍵合堆疊小晶片的超密集連接,博通的 3.5DXDSiP 採用 CoWoS-L 並結合 HCB 進行 F2F 邏輯堆疊,即指明了這一方向;混合鍵合不僅僅是一種特定的產品,而是一種多功能的賦能技術,它的採用可能會滲透到各種先進封裝架構中,全面提升密度和性能,而不是局限於單一「類型」的封裝。

應用案例展示:已部署 AI 加速器中的封裝解決方案

案例研究

- NVIDIA H100/Hopper:採用台積電 CoWoS-S 技術,整合 GPU 晶片與 HBM,主要應用於 AI 訓練和 HPC。

- NVIDIA Blackwell (B100/B200/GB200):轉向採用台積電 CoWoS-L 技術,以實現更大、更複雜的 HBM3e 整合。

- AMD Instinct MI300 系列 (MI300A/MI300X):採用台積電 SoIC 技術進行 CPU 和 GPU 晶片的垂直整合,然後再透過 CoWoS 技術與 HBM3 進行封裝,目標市場為 AI 和 HPC。

- Intel Ponte Vecchio (資料中心 GPU Max):採用 Foveros (3D 堆疊) 結合 EMIB (2.5D 橋接) 技術,構成了一個包含 47 個主動小晶片和 HBM 的複雜異質設計。

- Intel Meteor Lake:帶有 AI Boost NPU 的客戶端 CPU,採用 Foveros 的小晶片架構,整合 CPU、GPU、SoC 和 I/O 小晶片。

- Broadcom AI ASIC:利用 CoWoS-L 技術滿足深度學習和網路應用的需求,博通也在探索在 CoWoS-L 中應用混合鍵合技術。

- Apple M 系列 (未來 M5):預計將採用台積電 SoIC 技術進行先進整合。

封裝對 AI 訓練與推理晶片的影響

AI 訓練晶片(如 NVIDIA H100、AMD MI300X)通常需要最高的記憶體頻寬和容量,這推動了採用 CoWoS/SoIC 技術並整合多個 HBM 堆疊的趨勢。

AI 推理晶片,特別是邊緣運算推理晶片,可能更側重於成本和功耗效率;如果性能需求得到滿足,它們可能會採用複雜度較低的 Foveros 衍生版本或更早期的封裝技術;然而,資料中心的高性能推理應用同樣受益於先進封裝,有資料指出,CoWoS 目前對於智慧型手機 AI 而言成本效益不高,這表明可能需要考慮替代的封裝技術。

目前最強大的 AI 加速器實質上是複雜的系統級封裝 (SiP),其中封裝技術對性能的貢獻與晶片本身同等重要,封裝技術的選擇直接反映了針對特定 AI 工作負載所做的架構權衡;NVIDIA 的旗艦 GPU(H100、Blackwell)依賴 CoWoS 將大型 GPU 晶片與多個 HBM 堆疊整合,以最大化用於訓練的記憶體頻寬;AMD 的 MI300 則採用了更積極的異質整合方法,使用 SoIC 堆疊 CPU 和 GPU 小晶片,然後再透過 CoWoS 與 HBM 整合,展示了一種多層次的先進封裝策略;英特爾的 Ponte Vecchio 是一個極端的小晶片整合案例,同時使用了 Foveros 和 EMIB 來組合約 50 個小晶片,這些不僅僅是封裝中的晶片,封裝本身已成為系統整合平台;AI 晶片設計如今已與先進封裝設計密不可分,AI 加速器的性能、功耗和成本在很大程度上受到封裝選擇的影響,這促使晶片設計者與封裝專家之間進行更深入的合作。

可以觀察到一個明顯的趨勢:特定的封裝技術開始與特定類別的 AI 晶片或供應商產生關聯,但同時也出現了向混合鍵合技術融合的趨勢,視其為未來世代產品的終極賦能者;CoWoS 目前是高端資料中心 AI GPU(NVIDIA、基於 HBM 的 AMD 解決方案)的主力技術;英特爾的 Foveros 是其小晶片戰略的關鍵,已應用於其資料中心 GPU (Ponte Vecchio) 和支援 AI 功能的客戶端 CPU (Meteor Lake);所有主要參與者都已開始為其下一代旗艦產品採用混合鍵合技術(SoIC、Foveros Direct),例如:AMD MI300 中的 SoIC 組件、NVIDIA Rubin、Apple M5 以及 Intel Clearwater Forest,這表明,儘管當前世代的產品利用了已建立的先進封裝技術,但所有關鍵 AI 晶片供應商的路線圖都指向混合鍵合,以實現未來的性能飛躍;整個半導體生態系統(包括 EDA 工具、IP 供應商、測試設備)都必須與向混合鍵合發展的軌跡保持一致,以支援未來 AI 硬體的開發。

表 3:知名 AI 加速器及其封裝技術

|

AI 加速器 |

主要應用 |

主要封裝技術 |

主要整合小晶片 |

晶圓代工廠 |

|

NVIDIA H100 |

訓練、HPC |

TSMC CoWoS-S |

GPU + HBM |

TSMC |

|

NVIDIA B200 (Blackwell) |

訓練、HPC |

TSMC CoWoS-L |

GPU + HBM3e |

TSMC |

|

AMD Instinct MI300X |

訓練、HPC |

TSMC SoIC + CoWoS |

CPU + GPU + HBM3 |

TSMC |

|

Intel Ponte Vecchio |

AI、HPC |

Intel Foveros + EMIB |

多種計算/IO/記憶體小晶片 + HBM |

Intel/TSMC |

|

Intel Meteor Lake NPU |

客戶端 AI |

Intel Foveros |

CPU + GPU + NPU + I/O |

Intel/TSMC |

|

Apple M5 (預期) |

客戶端/伺服器 AI |

TSMC SoIC |

CPU + GPU + NPU (預期) |

TSMC |

|

Broadcom AI ASIC |

深度學習、網路 |

TSMC CoWoS-L (可能含混合鍵合) |

邏輯 + HBM (可能) |

TSMC |

未來展望與戰略建議

主要參與者路線圖 (台積電、英特爾、三星)

台積電 (TSMC)

- CoWoS 持續演進: 更大尺寸的中介層、支援更多 HBM 堆疊,並推出 SoW-X (System-on-Wafer) 等更先進的整合方案。

- SoIC (混合鍵合) 大力推進: 積極擴充 SoIC 產能,並已獲得 NVIDIA (Rubin 架構) 和蘋果 (M5 晶片) 等大客戶訂單,顯示其在下一代產品中的關鍵地位。

- 3DFabric™ 生態系統: 持續強化包含 CoWoS、SoIC、InFO 在內的 3DFabric™ 整合平台。

- 前瞻技術研發: 開發 A16 製程節點(採用超級電源軌 Super Power Rail 架構)、N2 製程節點(採用 NanoFlex™ 技術),以及用於矽光子整合的 COUPE™ 技術(與 SoIC-X 結合)。

英特爾 (Intel)

- Foveros Direct (混合鍵合) 積極發展: 持續微縮互連間距(<5µm,目標 3µm),將應用於未來的 Xeon 處理器 (如 Clearwater Forest) 及其他產品。

- Foveros 衍生技術擴展: 計劃於 2027 年推出 Foveros-R 和 Foveros-B 等新版本,以滿足更廣泛的應用需求。

- EMIB 技術增強: 擴展 EMIB 技術(如 EMIB-T)的應用。

- 製程與封裝協同: 將先進製程節點 (如 18A、14A) 與先進封裝技術 (如 18A-PT 結合 Foveros Direct) 緊密結合。

三星 (Samsung)

- X-Cube (混合鍵合) 路線圖: 基於微凸塊的 X-Cube 計劃於 2024 年量產,而無凸塊的 X-Cube(混合鍵合)則計劃於 2026 年量產。

- I-Cube 演進: I-CubeS (矽中介層) 已可支援 8 個 HBM,I-CubeE (嵌入式矽橋) 計劃到 2025 年可支援多達 12 個 HBM。

- 「超越摩爾」戰略: 持續專注於異質整合,推動先進封裝技術的發展。

AI 先進封裝新興趨勢 (Yole, TechInsights, SemiAnalysis 觀點)

- 2.5D/3D 封裝主導 AI 晶片: 市場預計將強勁增長,其中先進封裝市場年複合增長率 (CAGR) 約 10%,而高端性能封裝市場 CAGR 更可達 37%。

- 混合鍵合成為下一代關鍵: 對於 AI、5G、HPC 等應用,混合鍵合技術正變得不可或缺。

- 小晶片架構普及化: 小晶片設計將成為主流趨勢。

- 協同封裝光學 (CPO) 整合: 將 CPO 與 CoWoS、SoIC 等先進封裝技術結合,以實現極致頻寬。

- 面板級封裝 (PLP) 的潛力: 作為部分市場區隔的低成本高效益方案,未來可能應用於 AI/HPC 的超高密度扇出型封裝 (UHD FO)。

- 散熱管理持續創新: 針對高密度封裝系統的散熱挑戰,相關技術將不斷發展。

- 供應鏈格局演變: 晶圓代工廠 (TSMC, Intel, Samsung) 和 IDM 將引領先進封裝發展,OSAT 廠商則需積極適應。

對 AI 晶片設計者和系統架構師的關鍵考量

- 早期協同設計: 晶片、封裝和系統的早期協同設計至關重要。

- 多維度權衡: 需在性能需求、散熱限制、功耗預算和成本之間進行仔細權衡。

- 針對性選擇: 根據具體的 AI 工作負載需求(訓練 vs. 推理,資料中心 vs. 邊緣運算)評估不同封裝方案的優劣。

- 供應鏈考量: 了解所選封裝技術的供應鏈狀況和產能可用性。

- 面向未來設計: 考慮到向混合鍵合和小晶片生態系統(如 UCIe 標準 )發展的趨勢,進行前瞻性設計。

所有主要參與者的技術路線圖都將混合鍵合視為未來旗艦 AI 產品的關鍵賦能技術,這表明儘管目前仍存在挑戰,但業界對其必要性已達成廣泛共識。這將推動混合鍵合生態系統在研發和資本投入方面的大幅增長;台積電正積極推動 SoIC 技術應用於 NVIDIA 的 Rubin 架構和蘋果的 M5 晶片;英特爾的 Foveros Direct(混合鍵合)計劃用於未來的 Xeon 處理器(如 Clearwater Forest),並且是其 18A-PT 製程節點的核心組成部分;三星則目標在 2026 年實現無凸塊 X-Cube(混合鍵合)的量產;市場分析機構(如 Yole、TechInsights、SemiAnalysis)也一致強調混合鍵合對於未來 AI/HPC 的關鍵作用,整個半導體價值鏈,從材料和設備供應商到 EDA 工具開發商和 IP 提供商,都必須與向混合鍵合的轉型保持一致並提供支援,才能共同打造下一代 AI 硬體,早期參與混合鍵合設計規則和能力的開發,將成為一項重要的競爭優勢。

隨著封裝技術對 AI 晶片性能的影響日益加深,標準化工作(例如針對小晶片互連的 UCIe)對於培育更廣泛的生態系統以及管理來自多個供應商的異質整合的複雜性將變得越來越重要;異質整合涉及將可能來自不同設計者和晶圓代工廠的小晶片組合在一起;專有互連技術可能會限制互操作性並造成供應商鎖定。UCIe (Universal Chiplet Interconnect Express) 是一個開放標準,目的在標準化晶片間的通訊,在 CoWoS 和混合鍵合等先進封裝技術的支援下,UCIe 的成功採用可以簡化第三方小晶片的整合;Alphawave Semi 和 GUC 已經展示了基於台積電 CoWoS 的 UCIe IP,三星也是 UCIe 聯盟的創始成員之一。標準化可以讓 AI 晶片設計者專注於其核心競爭力,同時利用來自競爭市場的一流小晶片,所有這些都透過先進的封裝平台整合在一起,從而加速創新。這可能催生更多樣化和專業化的 AI 硬體解決方案。

結論

CoWoS、Foveros 和混合鍵合這三種領先的封裝技術,在推動 AI 晶片能力向前發展的過程中扮演著不可或缺的角色;CoWoS 以其成熟的 2.5D 整合方案,為當前高性能 AI 加速器提供了堅實的基礎,特別是在整合高頻寬記憶體方面;Foveros 則透過其 3D 堆疊技術,進一步提升了整合密度和性能,並在英特爾的產品線中得到應用;而混合鍵合,作為最具前瞻性的技術,憑藉其無凸塊直接連接的特性,預示著互連密度和功耗效率的又一次飛躍,被視為滿足未來 AI 極致需求的關鍵。

比較而言,CoWoS 的優勢在於其成熟的生態系統和較高的產能(儘管仍面臨需求壓力),但其 2.5D 結構在垂直整合密度上不及 3D 技術;Foveros 提供了 3D 堆疊,但在早期版本中面臨散熱和功率傳輸的挑戰,其衍生版本 Foveros Omni 和 Foveros Direct(混合鍵合)正致力於解決這些問題並提升性能;混合鍵合(包括台積電的 SoIC 和英特爾的 Foveros Direct)在互連密度、頻寬潛力和功耗效率方面擁有無可比擬的優勢,但其製造複雜度、成本和良率控制是當前需要克服的主要障礙,特別是對於異質整合至關重要的晶片對晶圓 (D2W) 製程。

展望未來,這三種技術並非簡單的替代關係,而更可能是一個共存互補、協同演進的局面;混合鍵合有望成為未來旗艦 AI 產品的核心互連技術,而 CoWoS 和 Foveros 的成熟衍生版本將繼續在各自擅長的領域服務於不同層級的 AI 應用;例如,透過混合鍵合技術(如 SoIC)高度整合的晶片系統,可以再利用 CoWoS 平台進行更大規模的系統級整合。

總體而言,先進封裝技術已經從傳統的配角轉變為半導體創新的核心支柱,尤其是在 AI 時代;隨著 AI 模型對算力和效率的永無止境的追求,封裝技術的持續突破將是決定未來 AI 硬體發展速度和上限的關鍵因素;對於 AI 晶片設計者和整個半導體產業而言,深入理解並戰略性地應用這些先進封裝解決方案,將是在這場技術革新浪潮中保持競爭力的不二法門。

奧創系統測試解決方案

奧創系統 (Ultrontek) 提供橫跨半導體製造與測試流程的關鍵解決方案;其產品組合包括:高精度的「晶圓處理平台 (EFEM)」,為自動化測試設備提供穩定可靠的晶圓傳送與定位;先進的「探針平台系統 (Probe Station)」,用於在封裝前對晶圓進行精密的電性量測,確保晶粒品質;以及用於最終可靠度驗證的「高溫壽命測試系統 (HTOL)」,透過長時間的高溫運作來模擬嚴苛環境,確保元件的長期耐用性與穩定度;從前端的晶圓級測試到後端的元件可靠度驗證,奧創的解決方案涵蓋了確保晶片效能與品質的關鍵環節。

參考資料

- 5th Gen CoWoS-S Extends 3 Reticle Size - WikiChip Fuse, https://fuse.wikichip.org/news/6031/5th-gen-cowos-s-extends-3-reticle-size/

- A Stacked CPU: Intel's Foveros - The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU - AnandTech, https://www.anandtech.com/show/15877/intel-hybrid-cpu-lakefield-all-you-need-to-know/2

- Advanced Package | Foundry | Samsung Semiconductor USA, https://semiconductor.samsung.com/us/foundry/advanced-package/

- Advanced packaging for high-end performance - Yole Group, https://www.yolegroup.com/yole-group-actuality/pushing-silicon-boundaries-advanced-semiconductor-packaging-for-high-end-performance/

- Advanced Packaging - TechInsights, https://www.techinsights.com/technology/advanced-packaging

- Advanced Packaging Innovations | Chip Packages - Intel, https://www.intel.com/content/www/us/en/foundry/packaging.html

- Advanced Packaging Market Monitor - Yole Group - Follow the latest trend news in the Semiconductor Industry, https://www.yolegroup.com/product/quarterly-monitor/advanced-packaging-market-monitor/

- Advanced packaging: How AI is revolutionizing the game - Yole Group, https://www.yolegroup.com/press-release/advanced-packaging-how-ai-is-revolutionizing-the-game/

- Advanced Semiconductor Packaging 2025-2035: Forecasts, Technologies, Applications, https://www.idtechex.com/en/research-report/advanced-semiconductor-packaging/1042

- Advanced semiconductor packaging: leading patent owners and new entrants - KnowMade, https://www.knowmade.com/technology-news/semiconductor-news/semiconductor-packaging-news/advanced-semiconductor-packaging-leading-patent-owners-and-new-entrants/

- AI Chip Market: Advanced Packaging Capabilities Key Differentiating Factor (TSMC CoWos), https://semiwiki.com/forum/threads/ai-chip-market-advanced-packaging-capabilities-key-differentiating-factor-tsmc-cowos.18447/

- AI Expansion – Supply Chain Analysis For CoWoS And HBM - SemiAnalysis, https://semianalysis.com/2023/07/26/ai-expansion-supply-chain-analysis/

- Alchip Reveals 3DIC Design Optimization Keys - SemiWiki, https://semiwiki.com/forum/threads/alchip-reveals-3dic-design-optimization-keys.21269/

- AMD Instinct™ Accelerators, https://www.amd.com/en/products/accelerators/instinct.html

- Chip Packaging Innovations: 2.5D vs. 3D Stacking Trends in 2024 (Latest Stats) | PatentPC, https://patentpc.com/blog/chip-packaging-innovations-2-5d-vs-3d-stacking-trends-in-2024-latest-stats

- CoWoS Capacity Set to Skyrocket by 2026: Massive Growth in ..., https://semiwiki.com/forum/threads/cowos-capacity-set-to-skyrocket-by-2026-massive-growth-in-advanced-packaging.21773/

- CoWoS, an unpopular technology 10 years ago, TSMC firmly dominates the AI chip market, https://www.creating-nanotech.com/en-US/newsc170-cowos-an-unpopular-technology-10-years-ago-tsmc-firmly-dominates-the-ai-chip-market

- CoWoS® - Taiwan Semiconductor Manufacturing Company Limited, https://www.tsmc.com/english/dedicatedFoundry/technology/cowos

- Cutting-edge Process Technologies for Data Center - Intel, https://www.intel.com/content/www/us/en/foundry/library/advanced-process-technologies-for-data-center.html

- Foveros - Intel - WikiChip, https://en.wikichip.org/wiki/intel/foveros

- Future R&D Plans - Taiwan Semiconductor Manufacturing Company Limited, https://www.tsmc.com/english/dedicatedFoundry/technology/future_rd

- Going Beyond the Limits with Advanced Heterogeneous Integration | Samsung Semiconductor Global, https://semiconductor.samsung.com/news-events/tech-blog/going-beyond-the-limits-with-advanced-heterogeneous-integration/

- Hybrid Bonding – Tomorrow's Interconnect - TechInsights Platform, https://library.techinsights.com/hg-asset/10147ff7-c189-4040-871f-a113cae34dc0

- Hybrid Bonding - Products & Technology | Besi, https://www.besi.com/products-technology/productgroup/hybrid-bonding/

- Hybrid Bonding Basics – What is Hybrid Bonding? - Brewer Science, https://www.brewerscience.com/what-is-hybrid-bonding/

- Hybrid Bonding Breakthrough for Faster AI and Computing Chips - Adeia, https://adeia.com/blog/the-future-of-faster-smaller-and-more-efficient-chips-a-breakthrough-in-hybrid-bonding

- Hybrid Bonding for Ultra-High-Density Interconnect - ResearchGate, https://www.researchgate.net/publication/378159846_Hybrid_Bonding_for_Ultra-High-Density_Interconnect

- Hybrid Bonding Process Flow – Advanced Packaging Part 5 - SemiAnalysis, https://semianalysis.com/2024/02/09/hybrid-bonding-process-flow-advanced/

- Hybrid Bonding Set to Transform the Semiconductor Industry - EE ..., https://www.eetimes.com/revamping-the-semiconductor-industry-with-hybrid-bonding/

- Hybrid Bonding Technology Market to Reach USD 756 Million by 2031, Driven by Demand for AI, 5G, and High-Performance Computing | Valuates Reports - PR Newswire, https://www.prnewswire.com/news-releases/hybrid-bonding-technology-market-to-reach-usd-756-million-by-2031-driven-by-demand-for-ai-5g-and-high-performance-computing--valuates-reports-302426555.html

- Hybrid Bonding: BE Semiconductor Leads the Charge in AI-Driven Chip Revolution, https://www.ainvest.com/news/hybrid-bonding-be-semiconductor-leads-charge-in-ai-driven-chip-revolution-241210102f490b0ae3acefe8/

- Hybrid Bonding: latest advancements 2.5D & 3D packaging industry – An interview with ADEIA - Yole Group, https://www.yolegroup.com/player-interviews/hybrid-bonding-latest-advancements-2-5d-3d-packaging-industry-an-interview-with-adeia/

- In the era of AI big models, Intel will continue to be a leader in advanced packaging, https://en.eeworld.com.cn/news/manufacture/eic693346.html

- Intel Advanced Packaging Technology Ensures High Quality & Reliability, https://cdrdv2-public.intel.com/826148/Volume%206%20Intel%20Advanced%20Packaging%20Technology.pdf

- Intel broadens product portfolio as it bids to win back foundry customer trust - DCD, https://www.datacenterdynamics.com/en/news/intel-wants-to-win-back-foundry-customer-trust-broadens-product-portfolio-and-launches-new-ecosystem-partnerships/

- Intel Delivers Cutting-Edge Process Technologies to the Data Center with Intel 18A and Advanced Chiplet Packaging, https://www.intel.com/content/dam/www/central-libraries/us/en/documents/2024-02/intel-tech-clearwater-wp.pdf

- Intel Foundry Gathers Customers and Partners, Outlines Priorities, https://newsroom.intel.com/intel-foundry/intel-foundry-gathers-customers-partners-outlines-priorities

- Intel Foundry Roadmap Update - New 18A-PT variant that enables ..., https://www.tomshardware.com/pc-components/cpus/intel-foundry-roadmap-update-new-18a-pt-variant-that-enables-3d-die-stacking-14a-process-node-enablement

- Intel Foundry Technology Bets: A Full-Stack Strategy for the Disaggregated Era, https://creativestrategies.com/research/intel-foundry-technology-bets-a-full-stack-strategy-for-the-disaggregated-era/

- Intel Mass Produces Foveros 3D: $3.5B U.S. Facility - Electronic Components Distributor, https://www.smbom.com/news/13166

- Intel, And Others, Inside - Semiconductor Engineering, https://semiengineering.com/intel-and-others-inside/

- Intel's Embarrassment of Riches: Advanced Packaging - EE Times, https://www.eetimes.com/intels-embarrassment-of-riches-advanced-packaging/

- Intel's Embarrassment of Riches: Advanced Packaging | SemiWiki, https://semiwiki.com/forum/threads/intel%E2%80%99s-embarrassment-of-riches-advanced-packaging.22430/

- Intel's First High-Volume Foveros Packaging Facility, Fab 9, Starts ..., https://www.anandtech.com/show/21246/intels-foveros-advanced-packaging-fab-9-starts-operations

- Intel's new 3D Foveros packaging tech: LEGO-like chiplets for CPUs, https://www.design-reuse-embedded.com/news/202208100/intel-s-new-3d-foveros-packaging-tech-lego-like-chiplets-for-cpus/

- Intel's Next Generation Packaging: EMIB and Foveros - Intel's ..., https://www.anandtech.com/show/16823/intel-accelerated-offensive-process-roadmap-updates-to-10nm-7nm-4nm-3nm-20a-18a-packaging-foundry-emib-foveros/4

- Intel's Roadmap Targets Through-silicon Via Issues in Foveros Technology - News, https://www.allaboutcircuits.com/news/intels-roadmap-targets-tsv-issues-in-foveros-technology/

- Left, Right, Above, and Under: Intel 3D Packaging Tech Gains Omnidirectionality, https://fuse.wikichip.org/news/3508/left-right-above-and-under-intel-3d-packaging-tech-gains-omnidirectionality/

- Meteor Lake - Wikipedia, https://en.wikipedia.org/wiki/Meteor_Lake

- [News] NVIDIA Reportedly Kicks off B300 Production Preparation in May, Boosting TSMC's 5nm and CoWoS-L - TrendForce, https://www.trendforce.com/news/2025/04/28/news-nvidia-reportedly-kicks-off-b300-production-preparation-in-may-boosting-tsmcs-5nm-and-cowos-l/

- [News] TSMC Reportedly Speeds Up AP7 and AP8 Build-Outs, Targets Doubling SoIC Capacity - TrendForce, https://www.trendforce.com/news/2025/03/26/news-tsmc-reportedly-speeds-up-ap7-and-ap8-build-outs-targets-doubling-soic-capacity/

- [News] Wafer-Level Packaging Showdown: TSMC Scales up CoWoS Reticle Size, as Intel Readies Foveros-S - TrendForce, https://www.trendforce.com/news/2025/05/02/news-wafer-level-packaging-showdown-tsmc-scales-up-cowos-reticle-size-as-intel-readies-foveros-s/

- Nvidia Secures Over 70% of TSMC's Advanced Packaging Capacity This Year - AInvest, https://www.ainvest.com/news/nvidia-secures-70-tsmc-advanced-packaging-capacity-year-2502/

- Nvidia, TSMC, and advanced packaging realignment in 2025 - EDN Network, https://www.edn.com/nvidia-tsmc-and-advanced-packaging-realignment-in-2025/

- Package | Technologies | Samsung Semiconductor USA, https://semiconductor.samsung.com/us/technologies/package/

- Panel Level Packaging 2025 - Yole Group - Follow the latest trend news in the Semiconductor Industry, https://www.yolegroup.com/product/report/panel-level-packaging-2025/

- PLP Technology Roadmap Toward High-end Packaging Fueled by AI, https://www.edge-ai-vision.com/2025/04/plp-technology-roadmap-toward-high-end-packaging-fueled-by-ai/

- Samsung Electronics Unveils Plans for 1.4nm Process Technology and Investment for Production Capacity at Samsung Foundry Forum 2022, https://semiconductor.samsung.com/news-events/news/samsung-electronics-unveils-plans-for-1-4nm-process-technology-and-investment-for-production-capacity-at-samsung-foundry-forum-2022/

- semianalysis.com, https://semianalysis.com/2024/02/09/hybrid-bonding-process-flow-advanced/#:~:text=Inspection%20and%20Metrology-,BESI%2C%20EV%20Group%2C%20AMAT%2C%20TEL%2C%20ASMPT%2C%20SET,to%20semiconductor%20manufacturing%20since%20EUV.

- Shaping the Future of AI Chips: Custom HBM and Advanced ..., https://semiwiki.com/forum/threads/shaping-the-future-of-ai-chips-custom-hbm-and-advanced-packaging-lead-the-way.21708/

- State-of-the-Art and Outlooks of Chiplets Heterogeneous Integration and Hybrid Bonding - Journal of Microelectronics and Electronic Packaging, https://imapsjmep.org/api/v1/articles/40307-state-of-the-art-and-outlooks-of-chiplets-heterogeneous-integration-and-hybrid-bonding.pdf

- The Future of Semiconductor Manufacturing: Trends in Advanced Packaging, https://www.formfactor.com/blog/2025/the-future-of-semiconductor-manufacturing-trends-in-advanced-packaging/

- The Pros and Cons of AI Chips: Weighing the Costs of Cutting-Edge Innovation, https://polyn.ai/the-pros-and-cons-of-ai-chips-weighing-the-costs-of-cutting-edge-innovation/

- Thermal and Power Delivery Challenges in 3D ICs - ResearchGate, https://www.researchgate.net/publication/226225629_Thermal_and_Power_Delivery_Challenges_in_3D_ICs

- Thermal Challenges and Advanced Cooling Opportunities for 2.5D and 3D High Performance Computing - IEEE Region 4, https://r4.ieee.org/cis-eps/?p=614

- TSMC debuts silicon technologies at its North America Technology Symposium - Optics.org, https://optics.org/news/15/5/6

- TSMC is becoming the lord of semiconductor packaging, in addition to foundry - Andy Lin, https://www.granitefirm.com/blog/us/2025/01/05/semiconductor-packaging-2/

- TSMC N2 + Next-Gen SoIC, Intel EMIB-T, Meta 3D Stacked Memory, CFET, 2D Materials, and More - SemiAnalysis, https://semianalysis.com/2025/02/05/iedm2024/

- TSMC Plans To Ramp Up SoIC Packaging Production By The End of 2025; NVIDIA's Rubin & Apple's M5 SoCs Are Expected To Feature The Standard | SemiWiki, https://semiwiki.com/forum/threads/tsmc-plans-to-ramp-up-soic-packaging-production-by-the-end-of-2025-nvidia%E2%80%99s-rubin-apple%E2%80%99s-m5-socs-are-expected-to-feature-the-standard.22411/

- TSMC Preps More Advanced Tools For AMD's MI300, Booming Sales Expected: Report, https://www.tomshardware.com/news/tsmc-preps-for-amd-and-nvidia-advanced-packaging-boom

- TSMC unveils advanced process in U.S. to meet AI chip demand - Focus Taiwan, https://focustaiwan.tw/business/202504240010

- TSMC's Advanced Packaging Capacity is fully booked for next two years by Nvidia and AMD, https://semiwiki.com/forum/threads/tsmc%E2%80%99s-advanced-packaging-capacity-is-fully-booked-for-next-two-years-by-nvidia-and-amd.20157/

- TSMC-SoIC® - Taiwan Semiconductor Manufacturing Company ..., https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/SoIC.htm

- TSMC 3DFabric Technology portfolio. SoIC: System on Integrated Chips - ResearchGate, https://www.researchgate.net/figure/TSMC-3DFabric-Technology-portfolio-SoIC-System-on-Integrated-Chips_fig1_386162569

- Understanding CoWoS Packaging Technology - AnySilicon, https://anysilicon.com/cowos-package/

- Understanding CoWoS: Cutting-Edge Advanced Packaging - Yunze, https://www.szyunze.com/understanding-cowos-cutting-edge-advanced-packaging/

- Unlock the Future of Advanced Packaging: A Deep Dive into Hybrid Bonding | TechInsights, https://www.techinsights.com/blog/unlock-future-advanced-packaging-deep-dive-hybrid-bonding

- Unveiling the Industry's First Silicon-Proven 3nm, 24Gbps UCIe™ IP Subsystem with TSMC CoWoS® Technology - Business Wire, https://www.businesswire.com/news/home/20240930428879/en/Unveiling-the-Industrys-First-Silicon-Proven-3nm-24Gbps-UCIe-IP-Subsystem-with-TSMC-CoWoS-Technology

- Unveiling the Logic Advanced Packaging Briefing - TechInsights, https://www.techinsights.com/blog/unveiling-logic-advanced-packaging-briefing

- Wafer-to-wafer hybrid bonding: pushing the boundaries to 400nm interconnect pitch - IMEC, https://www.imec-int.com/en/articles/wafer-wafer-hybrid-bonding-pushing-boundaries-400nm-interconnect-pitch

- What Intel Learned When an Elevator Smashed Into Its Supercomputer Chips - CNET, https://www.cnet.com/tech/what-intel-learned-when-an-elevator-smashed-its-supercomputer-chips/

- What Is Intel Meteor Lake and What Is Its AI Tools? - Premio Inc, https://premioinc.com/blogs/blog/what-is-intel-meteor-lake-and-what-is-its-ai-tools

- What's advanced packaging? It's a big way Intel Foundry hopes to dazzle, https://www.fierceelectronics.com/electronics/whats-advanced-packaging-its-big-way-intel-foundry-hopes-dazzle

- 1 Packaging Process Technology TSMC and Intel, CoWoS, EMIB, Foveros and Chiplets, https://www.youtube.com/watch?v=GfiaHEhFHaM

- 2.5D Packaging: Ultimate Guide - AnySilicon, https://anysilicon.com/2-5d-packaging-ultimate-guide/

- 32G UCIe Silicon on TSMC 3nm and CoWoS Technology - EE Times, https://www.eetimes.com/32g-ucie-silicon-on-tsmc-3nm-and-cowos-technology/