半導體長壽命的基石:JEDEC HTOL 測試與現代 IC 先進解決方案的全面分析

現代電子產品中可靠性的必要性

在當今高度互聯的世界中,半導體元件已從單純的計算組件演變為現代文明的基礎設施,從驅動自動駕駛車輛的人工智慧(AI)晶片,到維持全球通訊的數據中心伺服器,再到植入人體的醫療設備,電子系統的可靠性不再僅僅是一個品質指標,而是關乎安全、功能與信任的根本要求;現場失效(field failure)的代價是巨大的,不僅涉及產品召回和保修索賠的直接財務損失,更可能對品牌聲譽造成不可逆轉的損害,在汽車、航空航太或醫療等關鍵領域,其後果甚至可能危及生命安全。

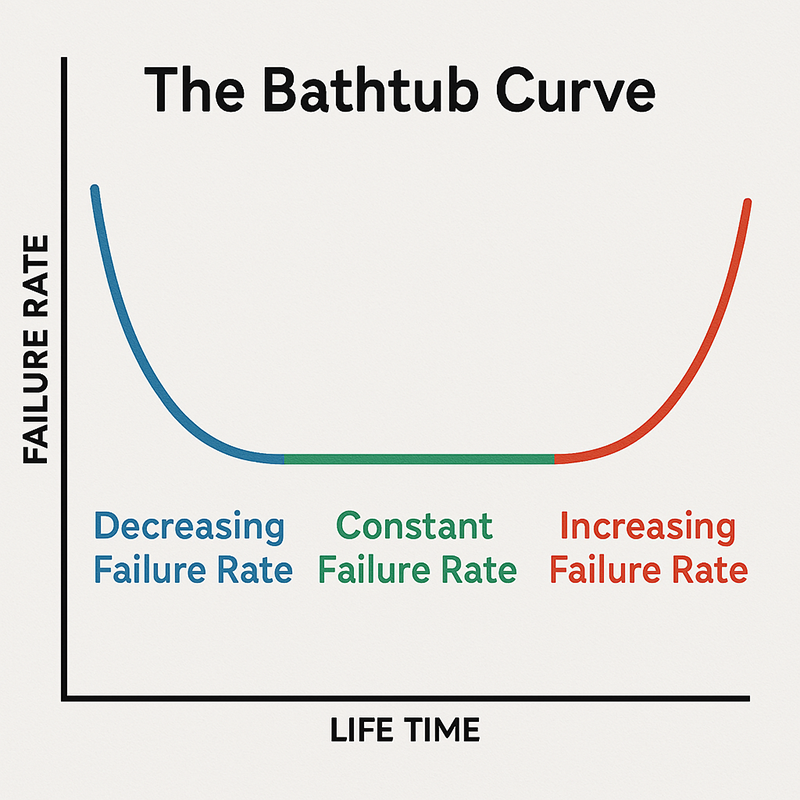

為了系統性地理解和預防這些故障,半導體產業普遍採用「浴盆曲線」(bathtub curve)模型來描述產品的生命週期故障率。此曲線分為三個階段:早期失效期(infant mortality)、偶然失效期(useful life)和耗損期(wear-out);早期失效通常源於製造過程中的隨機缺陷;偶然失效期代表產品穩定運行的階段,故障率較低且恆定;耗損期則是材料和元件因老化而開始系統性失效的階段,可靠性測試的核心目標,正是透過加速老化的手段,在產品出廠前識別並消除這三個階段的潛在失效模式,從而確保其在預期壽命內能夠穩定運行。

「浴盆曲線」(bathtub curve)模型

JEDEC 作為產業標準的領導者

在此背景下,一個權威、統一且被廣泛接受的標準化組織變得至關重要,固態技術協會(Joint Electron Device Engineering Council,簡稱 JEDEC)正是扮演此角色的全球領導者;JEDEC成立於1958年,最初的使命是為新興的半導體產業制定標準,確保不同製造商生產的二極體和電晶體等元件具有互換性,隨著時間的推移,其職責範圍已擴展至微電子產業的各個層面。

JEDEC 的核心使命是透過一個開放、自願且基於共識的流程來制定標準,其會員涵蓋全球近300家頂尖的半導體公司,包括製造商、設計公司和供應商,這種廣泛的代表性確保了其制定的標準能夠反映整個產業鏈的需求和最佳實踐,JEDEC 的影響力無所不在,其標準涵蓋了動態隨機存取記憶體(DRAM)模組(如 DDR5、LPDDR5)、靜電放電(ESD)防護、產品變更通知(PCN)以及至關重要的產品可靠性驗證方法,一個關鍵的特點是,JEDEC 的所有標準均可在其官網上免費下載,這極大地促進了其標準的全球普及和應用。

在 JEDEC 龐大的標準體系中,高溫工作壽命(High Temperature Operating Life,簡稱 HTOL)測試是可靠性驗證的基石之一,它被歸類於 JESD22 系列可靠性測試方法中,專門用於評估半導體元件在長時間高溫和電性偏壓下的穩定性,目的在加速並暴露那些由熱能啟動的潛在失效機制,從而預測元件在實際應用中的長期壽命。

然而,JEDEC 的運作模式也帶來了其固有的挑戰,其力量來源於其開放和共識驅動的流程——任何標準的通過都需要委員會三分之二多數的投票支持,且每家公司不論規模大小都只有一票投票權,這個為確保穩定性和廣泛接受度而設計的機制,在面對顛覆性技術創新時,其反應速度必然慢於單一企業的研發週期;這一點在寬能隙(Wide-Bandgap, WBG)半導體,如氮化鎵(GaN)和碳化矽(SiC)的興起中表現得尤為明顯,現有的、主要為矽基半導體設計的 JEDEC 標準,已多次被證實不足以完全描述 GaN 元件獨特的失效模式,這促使了新的專業委員會(如 JC-70)的成立,以彌補現有標準的不足;但這也表示在官方標準完全成熟之前,產業領導者必須採取「超越 JEDEC」(go beyond JEDEC)的策略,自行開發更為嚴苛的「測試至失效」(test-to-fail)方法,以確保其尖端產品的可靠性,這種在標準化與技術創新之間的張力,是理解現代半導體可靠性測試演進的關鍵。

JEDEC 可靠性驗證框架

半導體元件的可靠性是一個多維度的概念,單一的測試遠不足以全面評估其穩健性,因此,JEDEC 建立了一套名為 JESD22 的綜合測試方法系列,目的在從物理、電氣、機械和環境等多個角度,對封裝後的固態元件進行系統性的壓力測試,JESD22 系列的總體目標是透過施加加速應力,在實驗室環境中激發並沉澱出元件在實際使用中可能出現的各種失效模式,涵蓋了從晶片本身到封裝材料,再到兩者之間交互作用的各個層面。

這個框架並非一組孤立的測試,而是一種系統性的風險管理哲學,它隱含地承認,一個半導體元件是一個由矽、金屬、聚合物等不同材料構成的複雜系統,任何材料的特性或材料之間的介面都可能成為潛在的失效點;JESD22 測試套件的結構,正是對元件進行物理性解構,並針對每個潛在的失效領域設計相應的壓力測試,因此,可靠性工程師不僅僅是執行測試,他們遵循的是一套證明晶片電氣設計穩健性(HTOL)、封裝材料穩定性(HTSL)、組裝機械完整性(TC)以及對環境因素抵抗力(HAST)的完整方法論。

將 HTOL 置於關鍵可靠性測試之中

為了更清晰地理解 HTOL 的定位,有必要將其與其他幾項核心的 JESD22 可靠性測試進行比較和對照,這些測試共同構成了一個全面的驗證矩陣,確保產品在各種潛在威脅下的可靠性。

- HTOL (高溫工作壽命測試, JESD22-A108): 這是模擬元件實際工作狀態的測試,在施加動態電性偏壓(dynamic bias)的同時,將元件置於高溫環境中,其主要目標是加速由熱能和電場共同作用引發的晶片級(die-level)失效機制,例如電子遷移(electromigration)、電晶體老化(transistor aging)和時間相依介電質崩潰(Time-Dependent Dielectric Breakdown, TDDB)等。

- HTSL (高溫儲存壽命測試, JESD22-A103): 與 HTOL 不同,HTSL 僅施加高溫應力,而不施加任何電性偏壓,這個測試的目的是將封裝相關的失效機制與晶片電性相關的失效機制分開,它主要用於評估封裝材料(如環氧樹脂、引線框架)在高溫下的長期穩定性,暴露諸如材料降解、金屬間化合物(intermetallic compound)過度生長等問題。

- TC (溫度循環測試, JESD22-A104): 此測試讓元件在極端高溫和極端低溫之間反覆循環,其目的是模擬產品在運輸、儲存或實際工作(如開關機)中經歷的溫度劇變,這種應力主要針對由不同材料熱膨脹係數(Coefficient of Thermal Expansion, CTE)不匹配所引發的機械性失效,例如:晶片開裂、焊線(wire bond)斷裂、以及焊點疲勞等。

- HAST (高加速溫濕度應力測試, JESD22-A110): HAST 利用高溫、高濕度和高氣壓的組合,極大地加速濕氣沿著封裝材料的縫隙或介面滲透到晶片內部的過程,這項測試主要用於評估封裝的密封性和抗濕氣能力,其目標失效機制是金屬導線的腐蝕。

下表總結了這些關鍵可靠性測試的目的和目標失效機制,突顯了它們在整個驗證過程中的互補性。

表 1:JEDEC JESD22 關鍵可靠性壓力測試概覽

| 測試名稱 (標準ID) | 目的 | 典型條件 | 主要目標失效機制 |

|---|---|---|---|

| HTOL (JESD22-A108) | 模擬元件在加速條件下的長期工作壽命,評估電性與熱應力下的可靠性。 | 125°C, Vcc,max, 動態偏壓, 1000小時 | 電子遷移、電晶體老化、TDDB、熱載子注入。 |

| HTSL (JESD22-A103) | 評估元件在無偏壓高溫儲存環境下的長期穩定性。 | 150°C, 1000小時 | 封裝材料降解、金屬間化合物生長、參數漂移。 |

| TC (JESD22-A104) | 評估元件承受極端溫度變化的能力,檢測因CTE不匹配引發的機械應力。 | -50°C ↔ 150°C, 1000次循環 | 晶片開裂、封裝開裂、焊線斷裂、焊點疲勞。 |

| HAST (JESD22-A110) | 加速濕氣滲透,評估封裝在嚴苛溫濕度環境下的抗腐蝕能力。 | 130°C, 85% RH, 96小時, 施加偏壓 | 金屬導線腐蝕、參數失效。 |

| Preconditioning (JESD22-A113) | 模擬元件在表面貼裝技術(SMT)組裝過程中經歷的熱和濕氣應力。 | 烘烤、吸濕、迴焊 | 封裝分層(delamination)、爆米花效應(popcorning)。 |

通過這個全面的測試矩陣,JEDEC 確保了一個通過驗證的產品不僅能在其核心功能上穩定運行,還能承受製造、運輸和各種惡劣應用環境帶來的挑戰,HTOL 作為其中模擬真實工作狀態的核心測試,其結果對於預測產品的最終使用壽命至關重要。

深入解析 JESD22-A108:高溫工作壽命 (HTOL) 標準

JESD22-A108 標準是半導體可靠性驗證的支柱,其設計重點在提供一個標準化、可重複的方法,用以評估固態元件在長時間電性偏壓和高溫應力下的行為,它的重要性不僅在於產品的最終驗證,也貫穿於產品開發和生產監控的各個階段。

核心目標與範疇

HTOL 測試的首要目標是透過加速的方式,模擬元件在實際操作條件下的生命週期,從而確定其對熱與電聯合應力的抵抗能力,這項測試被廣泛應用於以下幾個關鍵領域:

- 新產品驗證 (Device Qualification): 對於任何新開發的積體電路(IC),通過 HTOL 測試是證明其設計和製程穩健性的基本要求。

- 可靠性監控 (Reliability Monitoring): 對於已量產的產品,定期進行 HTOL 測試可以監控生產過程中可能出現的變異,確保產品品質的一致性。

- 失效機制識別: 測試目的在加速並暴露那些由熱能啟動的潛在失效機制,例如熱載子注入(Hot Carrier Injection, HCI)、負偏壓溫度不穩定性(Negative Bias Temperature Instability, NBTI)以及前面提到的電子遷移和 TDDB。

- 早期失效篩選 (Infant Mortality Screening): 一種時間較短、有時應力更強的 HTOL 測試,通常被稱為「燒機」(burn-in),被用作生產線上的篩選工具;其目的是在產品出貨前,剔除那些因製造過程中隨機缺陷而可能在早期就失效的瑕疵品。

測試程式與參數

JESD22-A108 詳細規定了測試的執行條件,以確保結果的一致性和可比性,一個標準的 HTOL 測試流程包含以下關鍵參數:

- 偏壓條件 (Biasing Conditions): 為了最大程度地啟動晶片內部的潛在缺陷,測試要求對元件施加動態偏壓(dynamic bias),這表示需要提供時脈訊號和輸入向量,以驅動晶片內部最大數量的數位電路,並使類比電路在其全範圍內工作;至關重要的是,供電電壓通常設定為元件規格書中定義的最大操作電壓(Vcc,max),這通常比標稱電壓高出 5% 到 10%,目的是施加額外的電性應力,進一步加速老化過程。

- 溫度應力 (Temperature Stress): 測試在一個精確控制溫度的恆溫箱(oven)中進行;環境溫度通常設定為 125°C,對於更高可靠性要求的汽車或軍工級產品,溫度可能更高;高溫是主要的加速因數,它遵循阿倫尼烏斯方程(Arrhenius equation),即化學反應速率(在此指失效機制的進程)隨溫度的升高呈指數級增長;測試的目標是將元件的接面溫度(Junction Temperature, Tj)維持在一個穩定的高水準,因為 Tj 才是真正影響晶片內部物理化學反應的直接因素。

- 測試時長與讀點 (Duration and Readouts): 標準的驗證測試時長通常為 1000 小時,為了追蹤元件性能隨時間的衰退情況,標準通常要求在測試過程中設立中間讀點(interim readouts),例如在 168 小時和 504 小時進行,在每個讀點,會將元件從高溫環境中取出,待冷卻後進行全面的電性測試(ATE test),以檢查其功能和參數是否仍在規格範圍內。

- 測試樣本 (Test Samples): 為了確保測試結果具有代表性並能反映生產製造的正常變異,JESD47(積體電路應力測試驅動驗證的指導性檔)要求測試樣本必須來自至少三個(含)以上非連續的生產批次(lots),且每個批次的樣本數量應大致相等。

統計基礎與允收標準

HTOL 測試的結論並非僅僅基於工程判斷,而是建立在嚴格的統計學基礎之上,這賦予了其結果的客觀性和可信度。

- 樣本量與批次要求: 標準規定了最小的樣本數量,例如,一個常見的設定是每批次 77 個樣本,共 3 個批次;這個數量的選擇是基於統計抽樣理論,重點在於以一定的信心水準(Confidence Level, CL)確保產品的可靠性能夠達到預設的目標。

- 允收標準 (Acceptance Criteria): 對於驗證測試,最常見的允收標準是零失效(accept on zero failures),這表示在整個 1000 小時的測試過程中,所有測試樣本都必須通過每個讀點的電性測試。

- 信心水準與 LTPD: 樣本量和允收數量的組合與兩個關鍵的統計概念相關:信心水準(CL)和批次允收不良率(Lot Tolerance Percent Defective, LTPD),LTPD 指的是消費者願意容忍的批次中最大不良品率,例如,一個測試方案可能被設計為在 90% 的信心水準下,保證批次的不良率低於某個百分比(例如 1%),這代表如果一個批次的真實不良率高於 1%,那麼它有 90% 的機率無法通過這個抽樣測試;公式 χ2 = (2(C + 1) × LTPD)⁄N(其中 C 是允收失效數,N 是樣本量)可以用於計算這些參數之間的關係。

- 失效分析 (Failure Analysis): 在 HTOL 測試中,任何一次失效都不是簡單地被記錄為「不合格」,標準要求必須對失效的元件進行徹底的失效分析(FA),以找到失效的根本原因(root cause),這個過程至關重要,因為它提供了改進產品設計、製造工藝或封裝材料的直接回饋,是實現持續品質改進的閉環中不可或缺的一環。

下表根據汽車電子委員會(AEC)的 AEC-Q100 標準,將抽象的 HTOL 測試要求轉化為針對不同應用等級的具體測試條件,為工程師提供了實用的參考。

表 2:JEDEC JESD22-A108 (HTOL) 標準參數 (以 AEC-Q100 等級為例)

| 等級 (Grade) | 環境工作溫度範圍 (°C) | 典型 HTOL 測試溫度 (°C) | 典型測試時長 (小時) | 典型 Vcc 應力 |

|---|---|---|---|---|

| AEC-Q100 Grade 0 | -40 to 150 | 150 | 1000 | Vcc,max |

| AEC-Q100 Grade 1 | -40 to 125 | 125 | 1000 | Vcc,max |

| AEC-Q100 Grade 2 | -40 to 105 | 105 or 125 | 1000 (at 105°C) or 408 (at 125°C) | Vcc,max |

| AEC-Q100 Grade 3 | -40 to 85 | 85 or 105 | 1000 (at 85°C) or 408 (at 105°C) | Vcc,max |

總而言之,JESD22-A108 不僅僅是一份測試程式檔,它是一個結合了物理學、工程學和統計學的綜合性框架,為評估和確保半導體元件的長期可靠性提供了科學而嚴謹的基礎。

演變中的挑戰:現代 HTOL 實施的困境

儘管 JESD22-A108 的基本原則歷久彌堅,但半導體技術的飛速發展,特別是在功率密度、運算速度和材料科學方面的突破,已經將傳統的 HTOL 測試方法和設備推向了極限;過去數十年行之有效的測試平臺,在面對當今的尖端晶片時,顯得力不從心,接下來將探討現代 HTOL 實施所面臨的三大核心挑戰:功率與熱管理、寬能隙材料的興起,以及高速訊號的完整性,這三大挑戰並非孤立存在,而是相互交織,共同構成了一個複雜的工程難題。

高功率 IC 的熱與功率管理危機

隨著人工智慧、高效能運算(HPC)和 5G 通訊的蓬勃發展,現代的特殊應用積體電路(ASIC)、圖形處理器(GPU)和現場可程式化邏輯閘陣列(FPGA)的功耗已達到前所未有的水準,這種趨勢給 HTOL 測試帶來了兩個直接且嚴峻的挑戰。

功率傳輸的困境 (The Power Delivery Problem)

一顆先進的 7 奈米製程 AI 加速器在 HTOL 壓力條件下的功耗可能輕易超過 500 瓦,一個標準的 HTOL 測試板(或稱燒機板, Burn-in Board)上可能裝載數十顆這樣的待測元件(DUT),使得單一測試板的總功耗需求達到數千瓦;傳統的 HTOL 測試爐和燒機板通常採用集中式電源供應架構,其設計初衷是為功耗較低的元件服務,完全無法為如此巨大的負載提供穩定、純淨的電源;在 HTOL 的高溫環境下,僅僅是晶片的漏電流(leakage current)本身,就可能消耗或超過傳統測試系統的功率上限。

熱控制的挑戰 (The Thermal Control Challenge)

巨大的功耗必然伴隨著巨大的產熱;HTOL 測試的目標是將所有 DUT 的接面溫度(Tj)精確地維持在一個穩定的高水準(如 125°C),以確保加速因數的一致性;然而,當每個 DUT 自身就是一個數百瓦的熱源時,這項任務變得極其困難;如果沒有針對每個 DUT 的精確、獨立的熱管理,就會出現嚴重的問題:部分 DUT 可能因散熱不佳而產生熱失控(thermal runaway),導致過應力而提前失效;而另一部分 DUT 可能因過度冷卻而達不到目標溫度,導致應力不足,從而使測試結果失效;因此,採用帶有主動式冷卻(如風扇或液冷)的閉環溫度控制系統,已從一種選項變成了必需品。

妥協的後果 (The Consequence of Compromise)

面對這些功率和散熱的限制,可靠性工程師常常被迫做出妥協,例如降低供應電壓(Vcc)、減少施加在晶片上的動態測試圖樣(test pattern)的活動量,或者乾脆降低環境溫度;然而,正如一份針對 500 瓦 ASIC 的案例研究中所指出的,這些妥協「嚴重削弱了證明產品可靠性的能力」,因為降低了的應力水準可能不足以在有限的測試時間內(如 1000 小時)激發出關鍵的耗損型失效機制,這會給人一種產品非常可靠的假像,而實際上潛在的風險並未被暴露。

寬能隙 (WBG) 革命:新材料,新規則

以氮化鎵(GaN)和碳化矽(SiC)為代表的寬能隙半導體,憑藉其耐高壓、高頻開關和低導通電阻的優異特性,正在電力電子領域掀起一場革命。然而,這些新材料也帶來了傳統矽基半導體所沒有的、獨特的失效物理和可靠性挑戰。

超越矽的失效模式

GaN 和 SiC 元件的失效機制與矽有顯著不同,例如,GaN HEMT(高電子遷移率電晶體)中的動態導通電阻(dynamic RDS(on))現象、晶格缺陷引發的失效等,都是矽 MOSFET 中不常見的問題;因此,直接套用為矽開發的可靠性模型和測試方法,往往無法準確評估 WBG 元件的真實壽命和可靠性。

標準化的滯後

正如前文所探討的,JEDEC 標準的制定流程本質上是審慎而緩慢的,這導致了針對 WBG 元件的標準化進程相對滯後;雖然 JEDEC 成立了 JC-70 寬能隙功率電子轉換半導體委員會,並發布了 JEP173(動態導通電阻測試方法)、JEP180(GaN 功率元件開關可靠性評估)和 JEP182(連續開關測試方法)等指導性檔,但這些檔目前仍是作為對現有 JEDEC 框架的補充,而非完全取代。

「測試至失效」的必要性

由於標準的驗證測試(在規格書限制內進行)可能無法揭示 WBG 元件的真實操作極限和潛在的失效模式,產業內的領先製造商普遍採用了「測試至失效」(test-to-fail)的理念,這種方法論的核心是,刻意將元件推向超出其規格書極限的嚴苛條件下進行測試,直到產生大量失效為止,通過分析這些失效的根本原因,可以深入理解元件的內在失效機制(intrinsic failure mechanisms),從而建立更準確的壽命預測模型,並確定真實的可靠性裕度(reliability margin),而不僅僅是在單一應力點上獲得一個通過/不通過的二元結果。

應用相關的應力

對於一個用於開關電源的 GaN 功率電晶體,其 HTOL 測試若要具有實際意義,就必須盡可能地模擬其在真實應用(如升壓轉換器)中的工作狀態,即承受高頻、高壓的硬開關(hard switching)或軟開關(soft switching)應力,這對測試系統提出了全新的要求,它必須能夠提供並承受高壓、大電流的快速開關,這與傳統的針對邏輯元件的靜態或低頻動態偏壓有著本質的區別。

高速元件的訊號完整性要求

對於現代 SoC、FPGA 或通訊晶片而言,其價值和性能的核心在於高速的輸入/輸出(I/O)介面,例如 SerDes(串化器/解串器),對這類元件進行可靠性評估時,訊號完整性(Signal Integrity, SI)成為了第三個關鍵挑戰。

靜態 vs. 動態 HTOL

對於一個主要功能是高速數據傳輸的元件,僅僅施加一個靜態的直流偏壓(例如將所有輸入拉高或拉低)是遠遠不夠的,這種「靜態 HTOL」無法對最關鍵的高速收發電路施加有效的壓力;因此,「動態 HTOL」(Dynamic HTOL)成為必需,即在 HTOL 測試過程中,讓元件持續不斷地運行高速的數據模式(data patterns)。

挑戰所在

在 125°C 的高溫爐中,要將數十億位元每秒(Gbps)的高速訊號,從測試系統的訊號產生器,經過測試背板、燒機板、DUT 插槽(socket),精確無誤地傳輸到 DUT 的微小焊球上,然後再將其輸出訊號回傳進行監測,這是一項巨大的工程挑戰;高溫會改變傳輸線材料的介電常數和損耗,加劇阻抗不匹配、串擾(crosstalk)和電源雜訊(power supply noise)等問題,任何訊號的失真都可能導致測試失敗,而此時工程師將難以判斷問題是出在 DUT 本身,還是測試設備和治具上,從而使測試結果失去意義。

這三大挑戰——功率、熱和訊號完整性——並非各自獨立,它們共同構成了一個讓可靠性工程師頭痛的「絕望三角」,一個高功率的元件必然會產生嚴峻的熱管理挑戰,而同一個高功率、高效能的元件,幾乎可以肯定地會使用高速訊號進行通訊;因此,任何只解決了其中一個或兩個問題的方案都是不完整的;一個真正有效的現代 HTOL 測試解決方案,必須從系統架構的層面,同時應對這三個相互關聯的挑戰,這也解釋了為何傳統的測試設備在面對新一代半導體時會捉襟見肘,並為專業化、整合化的新一代測試平臺創造了市場機會。

先進測試方法學: HTOL 測試解決方案

面對現代半導體在 HTOL 測試中所呈現的複雜挑戰,市場需要的是超越傳統燒機爐概念的全新解決方案,接下來將從定義問題轉向提供一個全面的解決方案,介紹如何透過其先進的測試平臺,專門應對前文所述的功率、熱管理、寬能隙材料以及高速訊號完整性等難題,針對特定應用領域的痛點,採用高度整合的測試平臺。

解決功率與熱管理危機:整合系統方法

傳統 HTOL 測試系統的「一體適用」架構在面對高功率 IC 時已然失效,奧創系統的 HTOL 測試解決方案從根本上改變了這種架構,以應對超高功率元件的需求。

每 DUT 的獨立電源與控制

與傳統測試爐的集中式、共用式電源不同,奧創系統所提供的 HTOL 平臺架構能夠為每個 DUT 或小組 DUT 提供專用、可程式化的電源供應,這表示系統可以對每個元件進行精確的電壓控制、電流監測和過流保護,這種精細化的功率管理能力,對於安全、有效地測試像前文案例中提到的功耗超過 500W 的 ASIC 至關重要,它確保了每個 DUT 都能獲得穩定且符合要求的電性應力,避免了因電源不足而導致的應力妥協。

閉環熱管理系統

該解決方案超越了簡單的環境溫度控制,它整合了複雜的、針對每個 DUT 的獨立熱管理系統,系統透過溫度感測器,實現對每個元件溫度的即時監控,並透過閉環控制演算法動態調整冷卻系統的功率,從而將每個 DUT 的接面溫度精確地維持在目標值上,這種能力直接回應了在高功耗測試中維持有效且可重複應力條件的核心需求。

專注於高挑戰應用

奧創系統的技術藍圖為 AI、資料中心、汽車雷達和國防航太等領域,這些正是高功率和高熱密度挑戰最為尖銳的應用場景,所提供的解決方案是產業面對最緊迫問題的不二選擇。

超越通過/不通過:邁向原位參數監測

傳統的可靠性測試在 1000 小時結束後給出一個簡單的通過/不通過結論;然而,對於汽車和雲端運算等任務關鍵型應用,這種二元結果已遠遠不夠。產業需要更深入的數據來監測應力測試過程中真實的性能衰退效應。

新典範的推動者

奧創系統所提供的 HTOL 平臺正是這一新典範的關鍵推動者,透過將高精度的測量儀器(如精密電源、示波器、頻譜分析儀等)的能力整合到 HTOL 系統中,平臺能夠在測試過程中(in-situ)對 DUT 的關鍵參數進行連續監測;例如,對於一個功率電晶體,系統可以持續追蹤其漏電流、導通電阻(RDS(on))和開關時間的變化;對於一個 SerDes,則可以監測其眼圖(eye diagram)的張開度和抖動(jitter)。

原位監測數據的價值

這種方法提供了一個豐富的時間序列數據集,清晰地展示了每個元件在應力下的性能衰退軌跡和老化趨勢,它為可靠性工程師帶來了巨大的價值:

- 更準確的壽命預測: 通過外插這些衰退曲線,可以比傳統的單點失效數據更準確地預測產品的壽命。

- 早期發現設計邊際: 即使元件在 1000 小時後仍能「通過」測試,但如果其參數出現了顯著的早期衰退,這可能預示著設計上的邊際不足,原位監測可以及早發現這些問題。

- 加速根本原因分析: 當失效發生時,工程師可以立即回溯失效前一刻的詳細參數日誌,這極大地縮短了尋找根本原因的時間。

- 從「是否通過」到「裕度多少」: 這種方法論的轉變,使得可靠性測試從一個簡單的品質門檻,演變為一個提供深度工程洞察的過程,它完美地契合了產業對零缺陷和深度數據分析的追求。

奧創系統的產品策略是一個高度工程化、針對特定應用的「可靠性驗證平臺」,價值主張在於解決客戶在驗證和交付下一代旗艦產品時所面臨的最困難、最有價值的測試問題,滿足了那些視可靠性為核心競爭力的領先企業的需求。

結論:面向未來的可靠性測試戰略要務

本報告的分析清晰地揭示了一個核心趨勢:高溫工作壽命(HTOL)測試,雖然其根基於行之有年的 JEDEC 標準,但其實踐已從一個標準化的程式演變為一門複雜的、多面向的工程學科;半導體創新的不懈步伐,特別是在功率、速度和材料方面的指數級增長,已經在現代積體電路的需求與傳統測試方法及設備的能力之間,造成了一道巨大的鴻溝。

典範轉移

過去那種僅僅為了滿足標準要求而「勾選方塊」(checking the box)的 HTOL 測試時代已經結束,對於在汽車電子、人工智慧、高速通訊和國防航太等高風險、高價值領域競爭的企業而言,可靠性驗證不再是研發流程末端的一個成本中心,而是決定產品成敗和市場地位的戰略性差異化因素;這種轉變要求產業從根本上改變其測試理念,從傳統的靜態、二元(通過/不通過)測試,轉向能夠提供深度參數洞察的動態、應用相關的壓力測試;未來的可靠性工程師需要的不再是一個簡單的失效計數,而是在整個測試過程中,元件性能如何演變的詳細數據軌跡。

前瞻性建議

基於此,企業組織必須採取一種整體性、前瞻性的可靠性策略,這不僅僅代表著要深入理解 JEDEC 標準和針對特定技術(如 GaN)的新興指導方針的細微之處,更重要的是,要在測試平臺和方法論上進行戰略性投資。

最終的建議是,企業在規劃其下一代產品的可靠性驗證藍圖時,必須將測試平臺的選擇視為一項關鍵決策,選擇一個解決方案從設計之初就旨在應對當今乃至未來複雜的功率、熱管理和訊號完整性挑戰的測試合作夥伴和平臺,是確保產品成功、縮短上市時間並建立長期市場領導地位的關鍵一步,在可靠性決定一切的時代,投資於能夠看清未來挑戰並提供有效應對方案的測試能力,將是企業所能做出的最明智的投資之一。

參考資料

- High Temperature Testing Essentials - Number Analytics, https://www.numberanalytics.com/blog/high-temperature-testing-power-electronics

- Joint SAE/JEDEC GaN and SiC Working Group - TJ Green Associates LLC., https://tjgreenllc.com/wp-content/uploads/cmse/2024/presentations/Session%201B/1%20CMSE2024-Presentation-deLeon-Boeing.pdf

- High-Power Burn-In Testing in 2023: How to Overcome the Extreme | Smiths Interconnect, https://www.smithsinterconnect.com/smiths-interconnect-blog/high-power-burn-in-testing-in-2023-how-to-overcome-the-extreme/

- 4年一見JEDEC Workshops在台盛大舉辦 - 工商時報, https://www.ctee.com.tw/news/20191007700732-431298

- JEDEC - 維基百科,自由的百科全書, https://zh.wikipedia.org/zh-tw/JEDEC

- 固態技術協會JEDEC及工業標準JEDEC匯總介紹, http://qwctest.com/m/news_detail.aspx?id=819

- Reliability and Qualification | Cirrus Logic, https://www.cirrus.com/company/quality/product-development/reliability-qualification/

- JEDEC - JESD22-A108G - Temperature, Bias, and Operating Life - Standards | GlobalSpec, https://standards.globalspec.com/std/14574247/jesd22-a108g

- Reliability Qualification and Burn-In Services - EAG Laboratories, https://www.eag.com/services/engineering/burn-in-reliability/

- Establishing the reliability lifecycle tests of GaN power devices, https://www.powerelectronicsnews.com/establishing-the-reliability-lifecycle-tests-of-gan-power-devices/

- GaN HEMT Reliability: Why the Industry Can't Agree on One Testing Standard - News, https://www.allaboutcircuits.com/news/gan-hemt-reliability-why-the-industry-cant-agree-on-one-testing-standard/

- GaN Reliability and Lifetime Projections: Phase 15 - EPC Co, https://epc-co.com/epc/portals/0/epc/documents/product-training/Reliability%20Report%20Phase%2015.pdf

- JESD22 - Delserro Engineering Solutions, https://www.desolutions.com/testing-services/test-standards/jesd22/

- JEDEC STANDARD - Designer's Guide Community, https://designers-guide.org/forum/Attachments/JESD47G.pdf

- Overcoming Challenges of HTOL Bias-Life Testing of Ultra High-Power ASICs: A 500-Watt 7nm ASIC Case Study - ResearchGate, https://www.researchgate.net/publication/361070583_Overcoming_Challenges_of_HTOL_Bias-Life_Testing_of_Ultra_High-Power_ASICs_A_500-Watt_7nm_ASIC_Case_Study

- Qualification Test Method and Acceptance Criteria, https://www.issi.com/WW/pdf/qualtestmethod.pdf

- AEC-Q100-基於積體電路應力測試認證的失效機理 - 慶聲科技, https://www.kson.com.tw/rwd/pages/study_14-13.html

- 消費性IC設計業者如何切入汽車電子領域? 從解讀車用IC驗證標準AEC-Q100談起, http://www.sae.org.cn/touch/technicalDetail/pk/354

- The Guide to Semiconductor Reliability Testing - Accel RF, https://info.accelrf.com/semiconductor-reliability-testing-guide

- Aging characteristics of GanPower devices: HTOL high temperature aging test, https://iganpower.com/tektronix-advanced-semiconductor-laboratory-aging-characteristics-of-new-power-devices-htol-high-temperature-aging-test

- Achieving GaN Products With Lifetime Reliability - Texas Instruments, https://www.ti.com/lit/pdf/snoaa68

- Using Deep Data Analytics To Enhance Reliability Testing The Fast Roadmap for Zero Defects - Semiconductor Engineering, https://semiengineering.com/using-deep-data-analytics-to-enhance-reliability-testing-the-fast-roadmap-for-zero-defects/