矽之崛起:高階晶片的演進與全球半導體生態變革

數位時代的基石 - 從單晶片整合到架構分歧

下文一開頭將先提供半導體產業前幾十年發展的基礎技術與商業模式,說明在垂直整合模式下微處理器的崛起,隨後詳述向水準分工的無晶圓廠(Fabless)與晶圓代工(Foundry)模式的革命性轉變,此一轉變為後續的架構多樣化奠定了基礎。

微處理器的黎明與IDM的統治

接下來將詳細介紹微處理器的誕生及其早期發展所依賴的商業模式,為後續所有產業演進設定背景。

創世紀:Intel 4004,首款商用微處理器

1971年11月15日,英特爾(Intel)推出了Intel 4004,這不僅是一個新產品,更是一次典範轉移,它將電腦的核心功能,包括中央處理單元(CPU)、記憶體及輸出入控制,整合到一小組晶片上,其中4004是核心的處理單元。

在技術層面,4004的規格在當時是革命性的,它採用10微米(10μm)製程,在一個3mm x 4mm的晶片上整合了2,300個電晶體,時脈速度最高可達740 kHz,其運算性能與1946年推出、需要佔用整個房間的真空管電腦ENIAC相當,突顯了微型化技術的驚人飛躍。

這個改變時代的發明,其起源卻相當偶然,4004最初是為日本計算機公司Busicom的客製化專案而設計,英特爾工程師泰德·霍夫(Ted Hoff)的洞見,是將一個複雜的七晶片方案整合成一個更優雅且具成本效益的四晶片組(MCS-4),這個案例完美展示了特定應用需求如何催生通用技術的創新,當時,英特爾管理層將公司的主要業務定位於記憶體晶片,對此專案抱持懷疑態度,這也凸顯了革命性思想在其萌芽階段常被低估的現象。

IDM(整合元件製造)的霸權時代

在1980年代之前,半導體產業由整合元件製造(Integrated Device Manufacturer, IDM)模式主導,在此模式下,一家公司包辦從晶片設計、製程研發、晶圓製造、封裝測試到最終銷售的所有環節,英特爾是當時典型的IDM企業。

這種垂直整合模式在產業初期是必要的,設計與製造所需的龐大資本和緊密交織的專業知識,這代表只有大型整合公司才能參與競爭,此模式雖促進了快速創新,但也形成了極高的進入門檻,隨著1981年IBM個人電腦(PC)的問世,x86架構的成功進一步鞏固了IDM,特別是英特爾,長達數十年的市場主導地位。

摩爾定律:產業的經濟與技術引擎

由英特爾共同創辦人高登·摩爾(Gordon Moore)提出的摩爾定律,預測晶片上的電晶體數量大約每18至24個月會增加一倍,成為IDM時代成功的核心驅動力。

這一定律不僅是技術觀察,更成為一種自我實現的預言和產業的經濟模型,它保證了下一代晶片將以指數級速度變得更強大,且每個功能的成本更低,從而推動了創新與需求的良性循環,只要製程微縮能帶來可預測的指數級性能與成本改善,維持整個垂直整合體系所需的巨大資本支出就是合理的,並構成了一道難以逾越的競爭護城河;然而,當維持摩爾定律曲線的成本和複雜性變得高到讓多數廠商望而卻步時,此模式的弱點也隨之暴露。

世紀大分工 - Fabless-Foundry革命

接下來將闡述半導體產業史上最重大的結構性變革:從垂直整合走向水準專業分工的生態系統。

典範轉移:純晶圓代工模式的誕生

1987年台積電(TSMC)的成立,標誌著IDM絕對統治時代的終結,創辦人張忠謀精準地識別了市場的關鍵缺口,他分析了當時台灣的產業優劣勢,發現台灣具備強大的製造能力(當時在成熟製程上良率優異),但在IC設計與全球行銷方面相對薄弱,基於此他開創了「純晶圓代工」(Pure-Play Foundry)的商業模式——一家只為其他公司製造晶片,且絕不與客戶競爭的企業。

這個模式是革命性的,它將製造從一種專有資產轉變為一種可獲取的服務,大幅降低了晶片設計的巨大門檻,它所建立的「信任」與「不競爭」的夥伴關係,成為其最核心的價值主張與成功的基石。

設計者的崛起:無晶圓廠(Fabless)模式

晶圓代工模式的出現,催生了「無晶圓廠」(Fabless)公司的誕生——這類公司專注於設計和銷售晶片,但本身不擁有任何製造設施。

賽靈思(Xilinx)成立於1984年,被公認為全球第一家Fabless公司,它在台積電成立前,就已透過利用其他IDM的閒置產能,開創了此模式的先河,隨後,台積電和其他晶圓代工廠的崛起,為Fabless創新者的爆炸式增長提供了肥沃的土壤。

這次「大分工」實現了晶片設計的民主化,創新者可以將資本和人才集中在設計與市場行銷上,而將資本密集的製造環節交給專業的晶圓代工廠,這引發了一場晶片設計公司與新架構的「寒武紀大爆發」。

生態系的賦能者:IP與EDA

這個全新的、分工化的模式若要成功運作,離不開另外兩大關鍵支柱:

- 電子設計自動化(EDA):

現代晶片含有數十億個電晶體,其複雜度使得手動設計已無可能,EDA公司如新思科技(Synopsys)、益華電腦(Cadence)以及被西門子收購的明導國際(Mentor Graphics),提供了從邏輯設計、模擬到實體佈局與驗證等晶片設計各階段所需的關鍵軟體工具,商業EDA工具在1980年代的興起,是Fabless模式得以實現的先決條件,它提供了一套標準化的設計流程,讓設計成果可以順利地交給晶圓代工廠進行生產,這三家公司至今仍在EDA市場形成關鍵的寡佔地位。

- 矽智財(IP)核:

以安謀(Arm)為首的公司,開創了設計與授權處理器架構(IP核)而非直接銷售晶片的商業模式,Fabless公司可以向Arm獲取授權CPU核心、GPU核心或其他功能模組,並將它們整合到自己的系統單晶片(SoC)設計中,這極大地縮短了研發時間並降低了成本,Arm的商業模式包含一筆前期授權費和按每顆晶片收取的權利金,使其在無需承擔製造成本的情況下實現了大規模擴展。

這種產業結構的轉變,不僅僅是商業模式的創新,更深層次地反映了經濟與技術力量的演變,IDM模式的巨大前期投資,使其在面對不斷攀升的先進製程開發成本時,顯得愈發沉重,這種經濟壓力為專業分工創造了機會;晶圓代工廠的出現,讓製造規模化,而Fabless公司的崛起,則讓設計靈活化;EDA和IP供應商則成為了這個新生態系統中的「通用語言」和「標準化零件庫」,極大地提高了整個產業鏈的運作效率。

| 商業模式 | 核心功能 | 關鍵活動 | 優勢 | 劣勢 | 代表性企業 |

|---|---|---|---|---|---|

| IDM | 垂直整合 | 設計、製造、封裝、測試、銷售 | 技術整合度高、能率先導入新製程 | 資本支出巨大、營運模式僵化、產品線受限 | Intel、Samsung(早期)、Texas Instruments(早期) |

| Foundry | 專業製造服務 | 晶圓製造、製程研發、提供設計套件 | 專注製造、規模經濟、不與客戶競爭 | 資本極度密集、技術落後風險高 | TSMC、GlobalFoundries、UMC |

| Fabless | 晶片設計與銷售 | IC設計、市場行銷、產品定義 | 資本門檻低、專注創新、營運靈活 | 依賴代工產能、無製程主導權 | NVIDIA、AMD、Qualcomm、Apple、Xilinx |

| IP & EDA | 設計賦能 | 架構授權、軟體工具開發 | 高利潤率、輕資產營運、生態系核心 | 研發投入巨大、客戶高度集中 | Arm、Synopsys、Cadence、Siemens EDA |

為新運算世界而生的架構多樣化

隨著新生態系統的建立,產業得以自由地創造專用架構,以滿足個人電腦以外的新興市場需求。

系統單晶片(SoC)與行動時代

智慧型手機的崛起,催生了對一種不僅強大,而且體積小、高度整合且極度省電的晶片的需求,系統單晶片(SoC)應運而生,它在單一晶片上整合了CPU、GPU、記憶體、無線數據機(Wi-Fi、藍牙、蜂巢式網路)及其他多種元件。

SoC的概念最早可追溯至1974年的一款LCD手錶,但直到2000年代末期的智慧型手機革命才真正普及,這一時期的主要參與者及其策略包括:

- 高通(Qualcomm):

憑藉其整合了領先蜂巢式數據機技術的驍龍(Snapdragon)SoC,成為市場主導者,其商業模式結合了銷售晶片(QCT部門)與授權其龐大的無線技術專利組合(QTL部門),後者利潤極高。

- 蘋果(Apple):

從最初向三星採購,到2010年推出自行設計的A4晶片,蘋果憑藉其對硬體和軟體的雙重掌控,實現了無與倫比的性能與功耗表現,這種在Fabless模式下的垂直設計整合,為其後來的M系列晶片成功奠定了基礎。

- 聯發科(MediaTek):

透過提供高性價比、高度整合的SoC,迅速佔領了中低階智慧型手機市場,成為另一股重要力量。

GPU與平行運算的黎明

圖形處理器(GPU)最初是為處理3D圖形渲染這種高度平行的任務而設計,其架構擁有數千個簡單核心,與CPU專為序列任務設計的少數複雜核心形成鮮明對比。

2006年,輝達(NVIDIA)發布了CUDA(Compute Unified Device Architecture),這是一個革命性的平臺,將GPU的能力解放出來,用於通用計算(GPGPU),CUDA提供了一個軟體層,讓科學家和開發者能使用C++等熟悉的語言為GPU編程,而無需接觸複雜的圖形API。

這是一次戰略上的神來之筆,透過大力投資CUDA軟體生態系(函式庫、工具、開發者社群),NVIDIA建立了一道深厚的競爭「護城河」,即使競爭對手如AMD生產出性能強大的GPU,但由於缺乏一個成熟且被廣泛採用的軟體平臺與CUDA抗衡,使其難以在科學計算和AI領域獲得同樣的市場牽引力,CUDA最終成為高效能運算的實質標準。

開源替代方案:RISC-V的興起

RISC-V 是一個基於精簡指令集計算(RISC)原則的開源指令集架構(ISA)。

與Arm和x86等需要支付權利金的專有ISA不同,RISC-V可供任何人免費使用和修改,這種開放性與模組化特性促進了協作、降低了成本,並允許深度的客製化,企業可以針對特定工作負載添加自訂指令,而無需獲得許可或支付權利金。

在非營利組織RISC-V International的管理下,該架構正迅速在嵌入式系統、微控制器領域獲得關注,並開始向資料中心和AI等高效能應用領域發展,它對Arm在IP授權領域的主導地位構成了潛在的長期挑戰。

| 架構 | 設計哲學 | 主要應用 | 關鍵性能指標 | 主要參與者 |

|---|---|---|---|---|

| CPU | 低延遲、少數強大核心 | 序列處理、通用計算 | 時脈速度、每時脈週期指令數(IPC) | Intel、AMD |

| GPU | 高輸送量、數千簡單核心 | 平行處理、圖形、AI訓練 | 浮點運算效能(FLOPs)、記憶體頻寬 | NVIDIA、AMD |

| SoC | 整合度與功耗效率 | 行動裝置、嵌入式系統 | 每瓦性能(Performance-per-watt) | Apple、Qualcomm、MediaTek |

| AI加速器 | 領域專用、矩陣運算硬體 | AI推論/訓練 | 每秒兆次運算(TOPS)、每瓦TOPS | Google、AWS、各類新創 |

AI時代 - 重新定義高階晶片

接下來我們將聚焦於當前的技術紀元,人工智慧的需求成為高階晶片創新的主要驅動力,催生了新的架構和由大型科技公司主導的市場動態。

對智慧的無盡渴求 - 為AI而生的硬體

接下來將在AI的背景下定義現代高階晶片,並探討為這些工作負載而設計的專用硬體的崛起。

現代高階晶片的定義:AI伺服器

高階運算平臺的定義已從單一強大的CPU轉向一個異構系統,現代的AI伺服器是此轉變的典型代表,與主要依賴CPU的通用伺服器不同,AI伺服器結合了CPU與一個或多個強大的加速器,通常是GPU、專用ASIC(如Google的TPU)或FPGA。

這些伺服器在經濟上產生了巨大影響,一台搭載高階NVIDIA GPU的AI伺服器成本可能是一般伺服器的25倍以上,這不僅催生了一個龐大的新硬體市場,也為伺服器供應鏈帶來了繁榮,特別是為鴻海、廣達、緯穎等負責組裝這些複雜系統的台灣ODM廠商。

AI加速器的崛起:以Google TPU為例

雖然GPU被成功地應用於AI,但最高的效率來自於專為特定任務打造的硬體,這催生了AI加速器的崛起,這是一類專為神經網路核心數學運算而設計的特殊應用積體電路(ASIC)。

Google開發張量處理單元(Tensor Processing Unit, TPU)的動機源於內部需求,到2013年,其AI服務(搜尋、相簿、翻譯)的運算需求增長迅猛,以至於他們預計需要將資料中心的數量翻倍,這在成本上是不可持續的,因此,他們需要比市面上的CPU和GPU更高效的解決方案。

TPU的架構與CPU的設計理念截然不同,它犧牲了處理多樣化任務的複雜邏輯(如分支預測、亂序執行),轉而專注於一個巨大的矩陣乘法單元(MXU),該單元採用「脈動陣列」(Systolic Array)架構,這種設計最大化了數據的重複使用,並最小化了記憶體存取,從而在矩陣運算這一特定任務上顯著提升了性能和功耗效率。

第一代TPU於2015年秘密部署,它不僅是擊敗圍棋世界冠軍李世石的AlphaGo背後的功臣,更為Google的內部工作負載帶來了15至30倍的性能提升和30至80倍的能效提升,這一成果證明瞭領域專用架構的巨大價值,並引發了一場AI專用晶片的軍備競賽,此後,Google不斷反覆運算TPU,使其同時支援訓練與推論,並廣泛部署於其雲端和邊緣運算產品中。

這一轉變的深層邏輯在於,通用計算的時代紅利正在特定領域觸頂,當AI運算的需求規模化到一定程度時,使用通用硬體(CPU/GPU)的成本和效率瓶頸便凸顯出來,Google的TPU證明,透過放棄通用性換取特定任務的極致效率,是解決此問題的有效路徑,這代表了計算典範的一次重要回歸:從追求萬能的通用處理器,再次轉向為特定任務打造最高效工具的專用硬體。

雲端巨頭的豪賭 - 客製化晶片與自主設計

接下來探討大型科技公司(「雲端巨頭」或「Hyperscalers」)為優化其產品和基礎設施而自行設計晶片的趨勢,這從根本上改變了競爭格局。

蘋果的晶片戰略:終極的垂直整合

從2020年開始,蘋果公司在其Mac電腦產品線中,從英特爾CPU轉向使用內部設計的M系列晶片,這是一個分水嶺事件,這並非一蹴可幾,而是其為iPhone和iPad設計A系列SoC十多年經驗的結晶,蘋果早已建立起世界頂尖的晶片設計團隊,並精通於打造強大且高效的Arm架構SoC。

M系列晶片是SoC,而不僅僅是CPU,它在單一晶片上整合了CPU、GPU、用於AI的NPU(神經網路引擎)以及統一記憶體,由於蘋果同時掌控硬體(晶片)、裝置(Mac)和軟體(macOS),它能夠實現一種其他公司無法企及的優化水準;相比之下,微軟必須支援各式各樣的硬體,而英特爾則無法控制作業系統,這種緊密的整合帶來了每瓦性能的巨大優勢,重新定義了筆記型電腦的性能預期,為英特爾和Windows生態系統帶來了巨大壓力。

亞馬遜的雲端晶片:優化基礎設施堆疊

亞馬遜雲端運算服務(AWS),作為全球最大的雲端服務提供商,也在積極設計自己的晶片,以降低成本並提升其資料中心的性能。

- Graviton(CPU):

這是一款為通用雲端工作負載設計的Arm架構CPU,透過自行設計,AWS可以針對其基礎設施進行優化,提供比使用Intel或AMD的x86晶片更具性價比的雲端實例。

- Trainium(AI加速器):

這是AWS的客製化AI訓練晶片,目的在成為NVIDIA GPU的高性能、低成本替代方案,透過在Trainium上訓練像Anthropic的Claude這樣的大型模型,AWS不僅證明瞭其自研晶片的可行性,也為擺脫對NVIDIA的長期依賴奠定了基礎。

AWS的策略極為巧妙,它既是NVIDIA最大的客戶之一,在其雲端平臺上提供最新的NVIDIA GPU;同時,它又開發並推廣自己的晶片作為替代方案。這使其能夠在滿足當前客戶需求的同時,建立起長期的競爭威脅。

更廣泛的趨勢及其影響

蘋果、亞馬遜和Google的行動是更廣泛趨勢的一部分,雲端巨頭們正在為網路、視訊轉碼等特定的資料中心工作負載設計客製化ASIC,這對傳統晶片供應商如Intel和AMD構成了重大挑戰,因為他們最大的客戶如今也成了他們的競爭對手,雖然這些客製化晶片不在公開市場上銷售,但它們取代了巨大的潛在銷售量。

同時,這一趨勢也創造了新的機遇,像博通(Broadcom)和邁威爾(Marvell)這樣的公司,正透過與雲端巨頭合作設計這些客製化晶片(ASIC)而取得成功,扮演著設計服務夥伴的角色,而不僅僅是現成產品的供應商,AMD也在積極拓展此類半客製化業務。

技術前沿與地緣政治棋局

接著我們將探討半導體技術的最前沿 — 在製造和設計上被推向的物理極限 — 並將其與日益激烈的地緣政治競爭聯繫起來,後者現已成為定義該產業格局的關鍵因素。

挑戰物理極限 - 「後摩爾時代」的到來

隨著傳統的製程微縮速度放緩,創新的重心已轉向新材料、新電晶體結構以及新的晶片整合方式。

奔向埃米時代的競賽:先進微影技術

為了持續微縮電路特徵尺寸,半導體產業必須從深紫外光(DUV)微影技術轉向波長更短的極紫外光(EUV),這一轉變在技術上極其複雜且成本高昂;荷蘭 ASML是全球唯一能夠生產EUV微影設備的企業,這使其成為整個先進半導體生態系統中最關鍵的公司,沒有之一,一台EUV設備是人類製造過的最複雜的機器之一,售價超過1.5億美元。

目前,晶圓代工廠正競相導入2奈米(2nm)及更先進的製程節點,這不僅需要EUV,還需要下一代的高數值孔徑(High-NA)EUV設備。

- 台積電:

於2022年開始3奈米製程量產,目標在2025年實現2奈米量產,其技術藍圖已延伸至1.6奈米(A16)和1.4奈米(A14)。

- 三星(Samsung):

在2022年率先於3奈米節點導入GAA電晶體,但面臨良率挑戰,其目標同樣是在2025年進入2奈米製程,並在2027年達到1.4奈米。

- 英特爾:

正積極透過其「四年五節點」計畫追趕,目標使其20A(等同2奈米)和18A(等同1.8奈米)製程在2024至2025年具備量產能力。

電晶體的再想像:從FinFET到GAA

當電晶體尺寸縮小至20奈米以下時,傳統的平面(2D)電晶體結構因嚴重的「短通道效應」(漏電流)而難以為繼。

- FinFET(鰭式場效電晶體):

這種3D結構在22/16奈米節點被引入,它將導電通道豎立成垂直的「鰭狀」,使閘極能從三麵包覆通道,這提供了對電流更好的控制,成功將摩爾定律延續了近十年。

- GAA(環繞式閘極):

在3奈米/2奈米節點,即使是FinFET也達到了極限;下一步是GAA,其閘極完全環繞通道(以奈米線或「奈米片」的形式),這提供了終極的靜電控制能力,使進一步的微縮成為可能,三星在3奈米節點率先採用GAA,而台積電和英特爾則計畫在2奈米節點導入此技術。

Chiplet與先進封裝時代

隨著在先進節點上製造單一巨大晶片的成本變得極其昂貴且良率低下,業界正轉向基於小晶片(Chiplet)的設計方法。

Chiplet的概念是將一個大型處理器分解成多個較小的、功能專一的晶片,這些小晶片可以在不同的製程節點上製造(例如,高性能CPU核心使用3奈米,而I/O介面使用較成熟的7奈米),然後在一個封裝內重新組裝,這種方法可以提高良率、降低成本,並實現更靈活的模組化設計,AMD的Ryzen和Epyc處理器是此一策略的成功典範。

要實現Chiplet設計,需要先進的封裝技術來實現小晶片之間的高頻寬、低延遲互連。這已成為創新的新前沿。

- 台積電:

提供名為3DFabric的技術平臺,其中包括用於高階AI GPU的2.5D技術CoWoS(Chip-on-Wafer-on-Substrate),以及真正的3D堆疊技術SoIC(System-on-Integrated-Chips)。

- 英特爾:

擁有自己的競爭技術,包括2.5D解決方案EMIB(Embedded Multi-die Interconnect Bridge)和3D堆疊技術Foveros。

超越矽基:尋找新材料

展望未來,矽材料本身的物理極限已日益臨近,研究人員正積極探索新材料。

- 化合物半導體:

氮化鎵(GaN)和碳化矽(SiC)已在功率電子領域取得進展,提供比矽更高的效率、電壓和耐溫性,是電動車、快充和5G基礎設施的關鍵材料。

- 二維材料:

石墨烯(Graphene)和碳奈米管(CNT)展現出卓越的導電性和強度等誘人特性,但在大規模製造和整合方面仍面臨巨大挑戰。

| 晶圓代工廠 | 3奈米節點 | 2奈米節點 | 2奈米以下節點 | 關鍵技術 |

|---|---|---|---|---|

| TSMC | N3/N3E (2022) | N2 (2025) | A16/A14 (2026+) | FinFET (3nm), GAA-Nanosheet (2nm), 背面供電網路 (BSPDN) |

| Samsung | 3GAE/3GAP (2022) | SF2 (2025) | SF1.4 (2027) | GAA-MBCFET (多橋通道場效電晶體) |

| Intel | Intel 3 (2024) | Intel 20A/18A (2024/2025) | Intel 14A (2026) | FinFET (3nm), GAA-RibbonFET, PowerVia (背面供電) |

| 技術名稱 | 公司 | 類型 | 關鍵特徵 | 主要應用 |

|---|---|---|---|---|

| CoWoS | TSMC | 2.5D | 矽仲介層(Silicon Interposer) | 高階AI GPU、HPC |

| EMIB | Intel | 2.5D | 嵌入式矽橋(Silicon Bridge) | 高性能CPU/GPU |

| Foveros | Intel | 3D | 晶粒對晶粒(Die-on-die)堆疊 | 異質整合 |

| SoIC | TSMC | 3D | 晶圓對晶圓(Wafer-on-wafer)鍵合 | 高密度異質整合 |

| 項目 | 微處理器時代 | GPU與平行運算時代 | SoC系統單晶片時代 | AI加速器與特定領域架構 (DSA) 時代 |

|---|---|---|---|---|

| 時間跨度 | 1970年代 - 1990年代 | 1990年代末 - 2000年代 | 2000年代中 - 2010年代 | 2010年代中 - 至今 |

| 典範/驅動力 | 個人電腦(PC)革命 | 3D遊戲、科學運算、早期AI | 智慧型手機與行動裝置革命 | 深度學習、雲端運算、大型語言模型 |

| 高階定義/核心指標 | 電晶體數量、時脈速度 (MHz/GHz) | 平行處理能力、每秒浮點運算次數 (GFLOPS) | 功耗效率 (Performance-per-Watt)、整合度 | AI運算效率 (TOPS)、記憶體頻寬、能效 |

| 關鍵技術/架構 | • Intel x86 指令集 • 摩爾定律 |

• GPGPU (通用GPU) • NVIDIA CUDA 平臺 • 平行運算架構 |

• SoC (系統單晶片) 設計 • Arm 精簡指令集架構 • FinFET 3D電晶體 |

• ASIC (專用積體電路) • Chiplet (小晶片) 異質整合 • 先進封裝 (CoWoS, EMIB) • GAA 電晶體架構 |

| 代表性產品/公司 | • Intel (4004, 8086, Pentium) • Motorola |

• NVIDIA (GeForce, Tesla) • AMD (Radeon) |

• Apple (A系列晶片) • Qualcomm (Snapdragon) • MediaTek (天璣系列) • Arm (IP核心設計) |

• Google (TPU) • NVIDIA (資料中心GPU H100/B200) • AWS (Graviton, Trainium) • 台積電 (先進製程與封裝) |

| 商業模式 | IDM (整合元件製造) 模式主導 | Fabless (無廠設計) + Foundry (晶圓代工) 模式崛起 | • Arm的IP授權模式 成為核心 • Fabless + Foundry 成為主流 |

• 大型科技公司 自行設計晶片 • 地緣政治 驅動供應鏈區域化 • IDM 2.0 模式再起 |

矽的地緣政治新棋局

接下來將前述的技術與商業趨勢,整合到當前的地緣政治背景中,半導體已處於全球戰略競爭的核心。

晶圓代工戰爭:台積電 vs. 三星 vs. 英特爾

- 台積電的霸主地位:

憑藉超過60%的晶圓代工市佔率和在最先進節點上的近乎壟斷,台積電的成功建立在技術領先、卓越執行力以及備受客戶信賴的合作夥伴模式之上。

- 三星的挑戰:

作為唯一在先進節點上能與台積電匹敵的廠商,三星競爭激烈,但一直受制於不穩定的良率;此外,其自有產品部門(如智慧型手機)與潛在的晶圓代工客戶構成競爭關係,這種利益衝突是台積電極力避免的。

- 英特爾的IDM 2.0:

這是一項於2021年啟動、目的在重奪製造領先地位的大膽戰略,其三大支柱為:1)多數晶片仍由內部製造;2)擴大使用協力廠商晶圓代工廠(如台積電)生產部分Chiplet;3)成立「英特爾晶圓代工服務」(IFS),成為外部客戶的主要代工廠;這使英特爾處於一個與台積電既合作又競爭的複雜位置。

技術民族主義的興起

COVID-19疫情暴露了全球半導體供應鏈的脆弱性,而持續升級的美中緊張關係已將晶片轉變為關鍵的戰略資產。

- 美國《晶片與科學法案》:

一項規模達520億美元的標誌性法案,目的在將半導體製造、研發和人才培育帶回美國本土,該法案直接資助台積電、三星和英特爾在美國建設的新晶圓廠。

- 《歐洲晶片法案》:

一項類似的430億歐元計畫,目標在2030年前將歐盟在全球半導體生產中的份額翻倍至20%,重點發展製造與研發。

- 中國的「大基金」:

一個龐大的國家級投資基金(兩期基金加上地方政府配套資金,總額遠超500億美元),目的在實現半導體自給自足,特別是在成熟製程和化合物半導體等戰略領域,以對抗美國的出口管制。

- 日本的復興:

日本正大力投資重建其半導體製造基地,支援新成立的晶圓代工廠Rapidus,該公司目標與IBM和比利時微電子研究中心(imec)合作,生產2奈米晶片。

戰略意涵與未來展望

過去數十年由效率驅動的全球化供應鏈時代已經結束,一個以區域化、韌性和政治結盟為特徵的新時代正在形成,全球半導體產業的未來將由三股力量的相互作用所塑造:技術創新(GAA、Chiplet、AI硬體)、企業戰略(晶圓代工戰爭、雲端巨頭的豪賭)和地緣政治(晶片法案、出口管制)。

未來的關鍵戰場將圍繞以下幾點展開:完善2奈米及以下製程的競賽;提供最強大、最高效AI硬體的競爭;在先進封裝領域爭奪主導權;以及開源架構(RISC-V)與專有架構(Arm、x86)之間的長期博弈。

這背後存在一個根本性的矛盾:創造了高效但脆弱的半導體供應鏈的全球化邏輯,與試圖將其拆分和區域化的民族主義邏輯之間的緊張關係,企業被夾在中間,被迫在不同政府的衝突要求中航行;英特爾的IDM 2.0戰略正是這種緊張關係的縮影,它試圖在扮演美國國家冠軍的同時,又依賴全球合作夥伴並服務全球市場;對於像台積電這樣的領導者而言,這代表一場「多線作戰」:既要維持對三星和英特爾的技術領先,又要管理在美國、日本和德國等地的複雜建廠項目,同時還需應對日益嚴格的出口管制;如何駕馭這些相互衝突的壓力,是當前十年半導體產業領導者面臨的決定性挑戰。

結論

高階晶片的發展史是一部不斷追求微型化、更高性能和更低功耗的史詩,從Intel 4004將房間大小的電腦濃縮於方寸之間,到IDM巨頭憑藉摩爾定律統治PC時代,技術的演進始終是產業發展的主旋律;然而,真正重塑產業格局的是商業模式的革命,台積電開創的純晶圓代工模式,與Fabless、EDA和IP供應商共同構建了一個水準分工的創新生態系統,打破了IDM的垂直壁壘,催生了行動時代的SoC和AI時代的GPU等多元化架構。

如今,產業正進入一個由AI和地緣政治共同定義的新紀元,AI的龐大算力需求正驅動著從電晶體結構(GAA)、晶片設計(Chiplet)到系統架構(AI伺服器)的全方位創新;蘋果、Google和亞馬遜等科技巨頭憑藉其在軟體和應用端的優勢,向下整合至晶片設計,成為一股不可忽視的新興力量,直接挑戰傳統晶片供應商的地位。

與此同時,半導體已從純粹的經濟商品演變為國家安全的戰略核心,美國、歐盟、中國和日本等主要經濟體紛紛投入巨資,試圖重塑一個更具韌性但也更為割裂的區域化供應鏈,這場由政府主導的產業重組,正深刻改變著全球半導體的競爭規則與未來走向。

展望未來,高階晶片的競爭將不再是單一維度的賽跑,而是一場圍繞先進製程、AI專用硬體、先進封裝以及開放與封閉架構標準的立體戰爭,在這場技術、資本與政治交織的複雜棋局中,能夠駕馭多重挑戰、實現技術與戰略平衡的企業,才能最終在矽之巔峰立於不敗之地。

關於奧創系統

奧創系統科技的核心業務是提供高附加價值的工程整合服務,服務涵蓋初期諮詢、可行性研究、平臺評估、新舊技術整合,乃至最終的系統優化,公司立基於五大合作優勢:豐富的專案實績、整合新技術的卓越能力、協助客戶規避投資風險與節省時間的寶貴經驗、採用業界標準並客製非標方案的彈性,以及賦能客戶自主維護的完整技術轉移。

主要應用領域

奧創系統科技的專業技術服務橫跨多個尖端領域,展現其深厚的技術底蘊與市場洞察力:

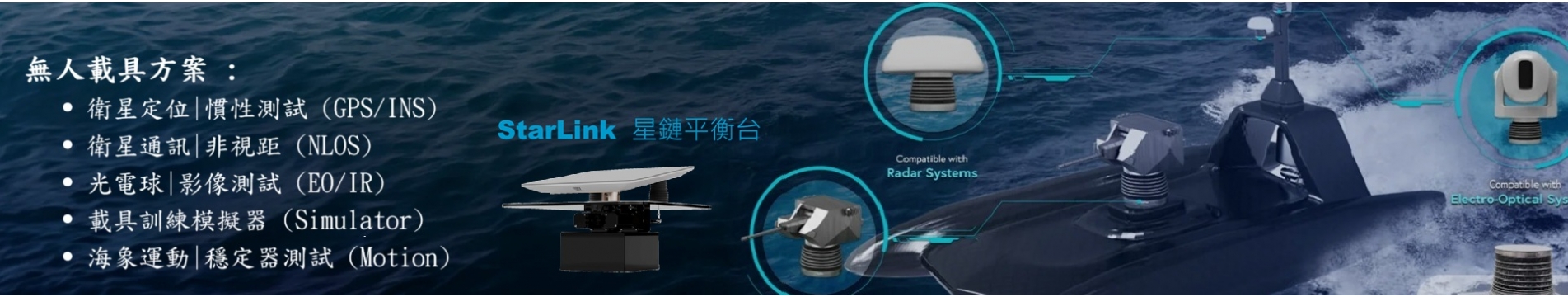

- 航太國防應用: 提供無人載具、訓練模擬器、衛星干擾防禦等關鍵系統。

- 半導體量測設備: 涵蓋探針平臺、高溫壽命測試 (HTOL) 等方案。

- 運動模擬平臺: 包含高精度六軸平臺與產業訓練模擬器。

- 射頻 (RF) 測試儀器: 從訊號產生、分析到完整測試系統建置。

- 光電影像模擬: 提供紅外線目標投影器、黑體校正源等專業設備。

- 車用製造 與 衛星測試: 針對新興的車用雷達與低軌衛星產業提供測試方案。

- 客製化系統:包含電波/電磁暗房建置與自動化軟體開發。

奧創系統科技不僅是設備供應商,更是能與客戶共同成長、持續創造雙贏的工程夥伴,以卓越的解決方案,驅動產業的創新力量。

參考資料

- Intel 4004 – 維基百科,自由的百科全書

- 「處理器」的今昔物語,超級比一比 - 國家實驗研究院

- 40年——微處理器發展史 - 51CTO

- 微處理器的發展簡史 - Around Physics 物理邊界

- intel 4004(世界上第一款微處理器) - jinzi - 博客園

- Intel 4004 - 維基百科,自由的百科全書 - 維琪百科 - Wikipedia

- 回顧歷史與審視現實,無晶圓產業走到頭了嗎? - 與非網

- IDM時代,終將過去? - 36氪

- IDM的歷史、發展過程、實用功能、應用領域及產業鏈結構原創 - CSDN博客

- 電子行業研究報告

- SoC系列之SoC歷史發展_soc晶片發展歷程 - CSDN博客

- 續摩爾定律看先進製程與封裝

- 台積電晶圓代工創新模式張忠謀回顧誕生過程 - 財富自由

- 企業核心價值與經營理念- 台灣積體電路製造股份有限公司 - TSMC

- 追求創新的先行者- 台積公司企業社會責任

- 賽靈思- 維基百科,自由的百科全書

- What is Electronic Design Automation (EDA)? – How it Works | Synopsys

- Understanding Electronic Design Automation (EDA): A Comprehensive Overview - Arshon Inc. Blog

- How Synopsys and Cadence are fueling the semiconductor industry's growth engine

- シノプシス(SNPS)- EDAツールで業界トップシェアかつIPベンダーでも2位 | アメリカ部

- ARM Processors and ARM Holdings: A Revolutionary Business Model - Poly Electronics

- ARM Business Model - Strategyzer

- 什麼是系統單晶片(SoC)? - Ansys

- 系統級晶片(SoC)的演進:從早期手機到邊緣智能

- 手機SoC晶元發展歷程回顧

- 手機soc廠商自研架構成趨勢 - 钜亨號

- Qualcomm Business Units, Vision, & Technology Roadmap

- Here's How Qualcomm Makes Its Money | The Motley Fool

- Apple M-series chips and the future of the semiconductor industry - PreScouter - Custom Intelligence from a Global Network of Experts

- cuda的發展歷史和作用 - CSDN博客

- CUDA 總複習:回顧GPU 運算的起源- NVIDIA 台灣官方部落格

- NVIDIA發展史關鍵事件時間軸 - MyLens AI

- CUDA Zone - Library of Resources | NVIDIA Developer

- CUDA - Wikipedia

- CUDA - 維琪百科,自由的百科全書

- CUDA - 維基百科,自由的百科全書

- AMD's Ryzen AI Max+ 395 Chip is Game Changer in Desktop AI, That Positions AMD Stock as a Premier AI Investment | User | chroniclejournal.com

- Prediction: These 2 AI Chip Stocks Will Outperform Nvidia Over the Next 5 Years - Nasdaq

- What is RISC-V and why is it important?

- RISC-V Architecture: A Comprehensive Guide to the Open-Source ISA - Wevolver

- RISC-V - Wikipedia

- AI伺服器是什麼?概念股有哪些?AI伺服器懶人包:龍頭是 ... - 數位時代

- 起底穀歌TPU的發展史-虎嗅網

- Google TPU的發展歷程與思考(一) 原創 - CSDN博客

- 【AI系統】穀歌TPU 歷史發展-騰訊雲開發者社區

- 人工智慧加速器- 維基百科,自由的百科全書

- How did Apple get Apple silicon so good so quickly? : r/macbookpro - Reddit

- Five years of Apple Silicon: How Apple continues to revolutionize chips - Current Mac Hardware Discussions on AppleInsider Forums

- M2 Max: Under the Hood With the Latest Apple Silicon - Creative Strategies

- Amazon is Selling NVIDIA's Chips While Offering Alternatives to It - Analytics India Magazine

- AWS is working on new Graviton and Trainium chips as an alternative to Nvidia - Techzine

- [News] Amazon Unveils New AWS-Designed Chips, Boosting Orders for TSMC and ALCHIP

- AI Accelerator - AWS Trainium

- Are you concerned About Hyperscalers Designing Their Own Chips? : r/AMD_Stock - Reddit

- Data Center CPU Dominance Is Shifting To AMD And Arm - Semiconductor Engineering

- 半導體微影製程設備新興技術發展與產業觀察 - 經濟部

- 奈米世代微影技術之原理及應用 - CTIMES

- 市場變局:ASML近期重大發展與挑戰 - 方格子

- 夢想進入ASML?這些技能讓你脫穎而出成為半導體界的明日之... - 工程師學習

- 半導體製程重中之重-微影技術的突破與創新 - 機械工業雜誌

- 美中衝突正重塑半導體產業,改變ASML未來也衝擊產業創新

- EUV(極紫外光微影技術)主要應用的製程節點 - 方格子

- 2nm Technology - Taiwan Semiconductor Manufacturing Company Limited

- [News] Global Acceleration in the Construction of 2nm Wafer Plants - TrendForce

- TSMC's says 1.6nm node to be production ready in late 2026 — roadmap remains on track

- 2奈米製程有望徹底改變半導體產業,2025年台積電和三星將在此較量

- Samsung updates process technology roadmap: 2nm in 2025, 1.4nm in 2027 - EEWorld

- 2 nm process - Wikipedia

- 利用薄膜轉印製作垂直堆疊閘極環繞互補式電晶體的設計與製程 - 華藝線上圖書館

- GAA + BSP = 後摩爾時代雙引擎?解密台積電、Intel 如何靠「電晶體架構」與「供電革新」續命摩爾定律 - AmiNext

- GAA晶體管時代即將開啟? - Moomoo

- AMD全面採用chiplet小晶片技術而獲得了技術優勢 - 科技產業資訊室

- 半導體小晶片(Chiplet)模式暨異質整合封裝發展趨勢 - 經濟部

- 打造次世代效能的小晶片市場 - Arm

- 10倍成長!!! 『小晶片』市場的驚人潛力 - 方格子

- TSMC 3DFabric™: Industry-leading 3D Silicon Stacking and Advanced Packaging Technologies - YouTube

- [News] The Era of Heterogeneous Integration Approaches: Who Shall Dominate the Advanced Packaging Field? - TrendForce

- Intel's Embarrassment of Riches: Advanced Packaging - EE Times

- Intel's Embarrassment of Riches: Advanced Packaging | SemiWiki

- Moving Beyond Silicon - Corporate News - Cadence Blogs

- What Lies Beyond Silicon: The Future of Advanced Electronics Materials - Bis Research

- The future of semiconductor materials: Beyond silicon - Electronics360 - GlobalSpec

- Beyond Silicon — What Is the Next Big Thing After Silicon Chips? | by Infinita Lab | Medium

- (PDF) BEYOND SILICON: EMERGING MATERIALS AND TECHNOLOGIES IN SEMICONDUCTOR INNOVATION - ResearchGate

- Beyond Silicon — The Future of Semiconductors and the Search for Next-Generation Materials | by RocketMe Up I/O | Medium

- 2025年,台積電的產能佈局如何改變全球半導體格局? - 最新消息- 新聞訊息

- 全球晶圓代工頂尖對決,台積電全面勝出 - 遠見雜誌

- 晶圓代工廠2奈米爭霸賽台積電獨霸三星、英特爾優劣全說了 - 工商時報

- 韓媒不忍了曝殘酷差距!揭三星苦追不上臺積電「關鍵」 - 自由財經

- MIC AISP Intel IDM 2.0策略剖析

- 英特爾揭示IDM2.0新策略三大面向一次看 - DigiTimes

- 英特爾『IDM 2.0戰略』斥資200億美元重振半導體製造業

- 【KT 新聞選讀】IDM 2.0 逐漸具體化,Intel 藉晶圓代工與跨架構設計,增加潛在市場規模

- A World of Chips Acts: The Future of U.S.-EU Semiconductor Collaboration - CSIS

- Confronting China and Catching Up on Chips - CEPA

- Japan and the European Chips Act – EIAS

- China's Quest for Semiconductor Self-Sufficiency | Centre for Emerging Technology and Security

- Lessons for Europe from China's quest for semiconductor self-reliance - Bruegel

- Can Rapidus Achieve Japan's Semiconductor Revival? - The Diplomat

- Semiconductors have a big opportunity—but barriers to scale remain | McKinsey