DisplayPort 物理層一致性與訊號完整性測試方案

從標準一致性到深度除錯:駕馭高速 DisplayPort 設計的複雜挑戰

隨著現代顯示技術對頻寬的需求不斷增長,DisplayPort (DP) 已成為主流的高速數位顯示介面,從 HBR3 的 8.1 Gbps 到 DP 2.1 時代的 UHBR20 (每通道 20 Gbps),飛快的傳輸速率使得訊號完整性成為設計與驗證中最關鍵的挑戰。

為了確保不同廠商的設備之間能夠無縫互通,視訊電子標準協會 (VESA) 透過其一致性測試規範 (Compliance Test Specification, CTS),為發送端 (Source)、接收端 (Sink) 及線纜的性能驗證,制定了嚴格的測試程序,一套完整且可靠的測試解決方案,不僅是通過認證的必要條件,更是加速產品開發、降低整合風險的關鍵。

一套完整的 DisplayPort 測試環境

一個典型的 DisplayPort 測試物理鏈路包含三個核心元件:

- 發送端設備 (Source/Transmitter):產生並傳送高速主鏈路 (Main Link) 數據。

- DisplayPort 線纜 (Passive Channel):在源與匯之間傳輸訊號,但同時也可能帶來插入損耗、反射等訊號衰減。

- 接收端設備 (Sink/Receiver):接收並解碼傳輸訊號。

此解決方案聚焦於發送端的一致性測試與線纜的特性分析,提供從自動化標準測試到深度訊號完整性除錯的完整流程。

第一部分:發送端 (Source) 測試

測試點 (Test Points) 的定義

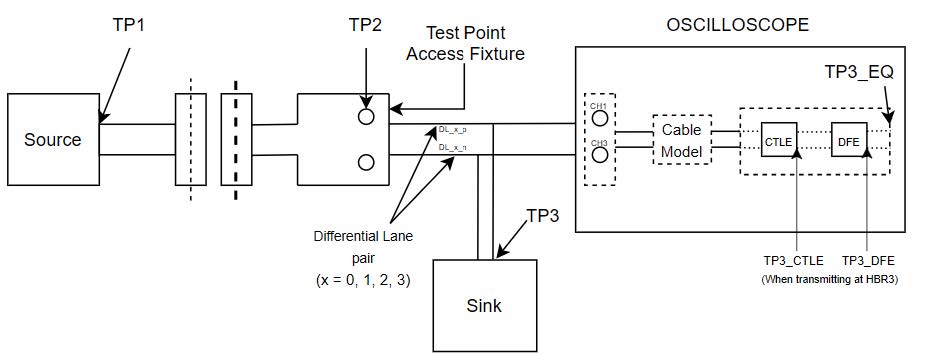

VESA 為 DisplayPort 標準定義了一系列的測試點 (TP),作為評估訊號完整性的標準化位置。

Figure 1: 測試點 (TP) 定義

- TP1: 位於發送端晶片封裝的輸出引腳,僅為參考點,無法實際量測。

- TP2: 位於測試治具 (TPA Fixture) 上,盡可能靠近發送端的連接器,這是所有發送端測試的規範性量測點,用於量測電壓擺幅、眼圖、抖動等。

- TP3_EQ / TP3_CTLE / TP3_DFE: 這些是基於 TP2 量測結果的計算測試點。

示波器會透過嵌入一個最差情況的線纜模型,並套用接收端等化器 (CTLE/DFE) 演算法,來模擬訊號在接收端晶片輸入端的樣貌。

示波器在此扮演了一個「參考接收機」的角色,用以評估訊號在經歷最差傳輸路徑後,是否仍能被正確解讀。

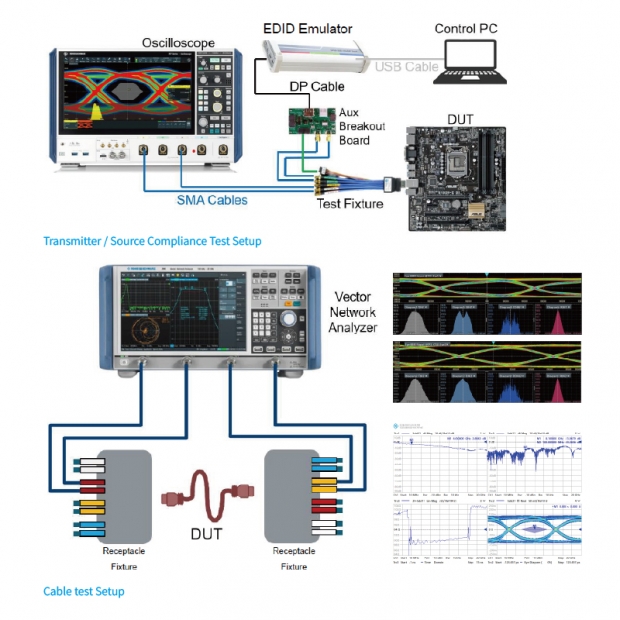

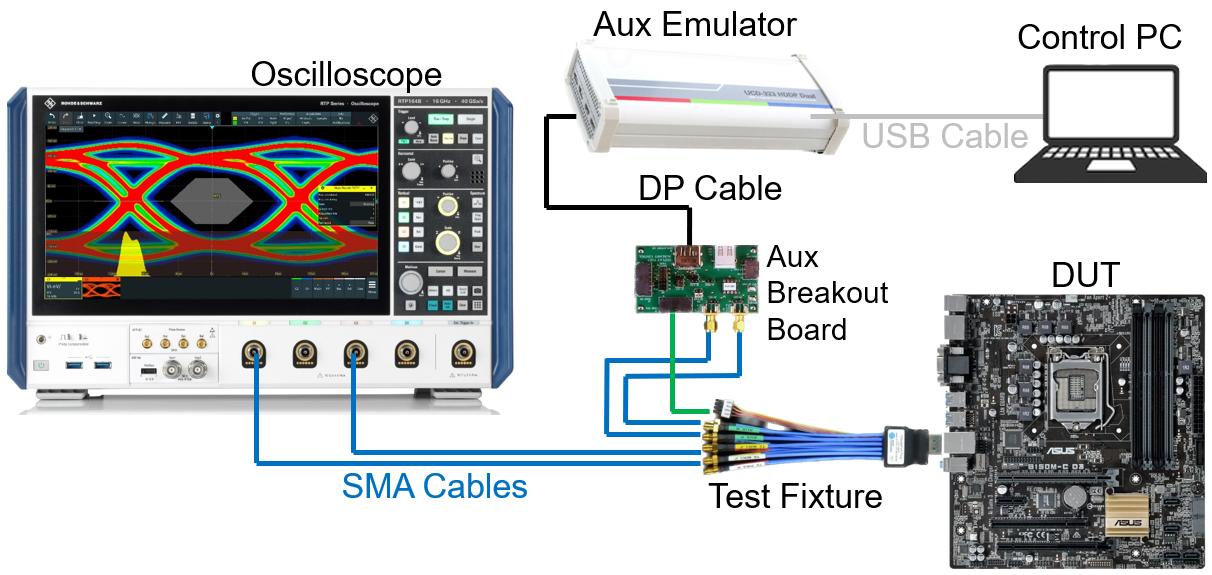

發送端一致性測試設置

一個典型的 DisplayPort 發送端測試,是將待測物 (DUT) 透過專用的測試治具連接到高性能示波器,以擷取 TP2 的訊號,AUX 通道則透過一個輔助板連接到 EDID 模擬器,用以觸發待測物進入指定的測試模式(如設定解析度、通道數、傳輸速率等)。

Figure 2: 發送端 (Source) 一致性測試設置

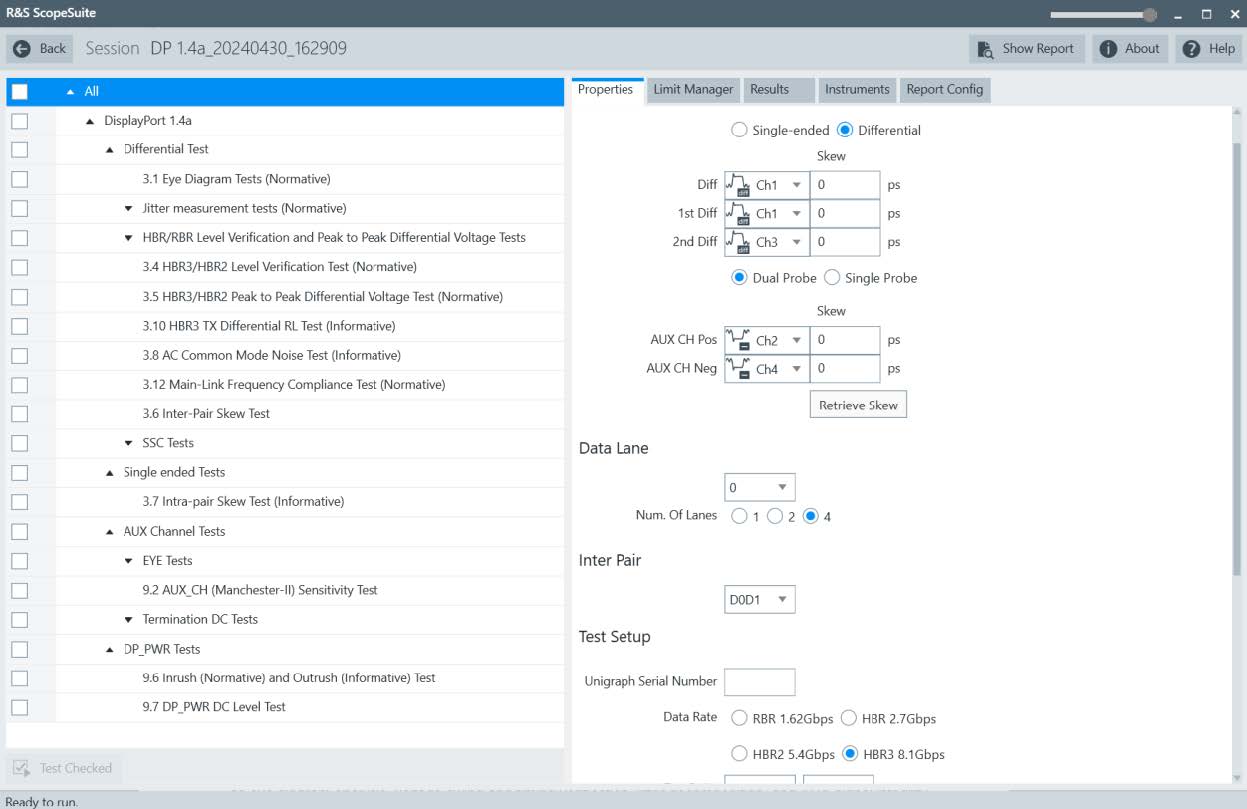

使用 R&S ScopeSuite 實現自動化一致性測試

DisplayPort CTS 規範了包含眼圖分析、電壓與時序、抖動分解、AUX 通道完整性等一系列繁瑣的物理層量測,為了提升效率與一致性,自動化測試軟體至關重要。

R&S ScopeSuite (RTP-K114) 軟體提供了一個結構化的工作流程,能引導進行設定、自動執行所有 CTS 定義的測試項目,並生成包含 Pass/Fail 結果、波形圖、眼圖與抖動分析的完整報告,大幅縮短測試時間並確保結果的可重複性。

Figure 3: R&S ScopeSuite 軟體介面

當一致性測試失敗時:進階訊號完整性驗證與除錯

若自動化測試的結果不通過或處於及格邊緣,就需要手動進行更深入的訊號完整性分析,以找出問題根源。

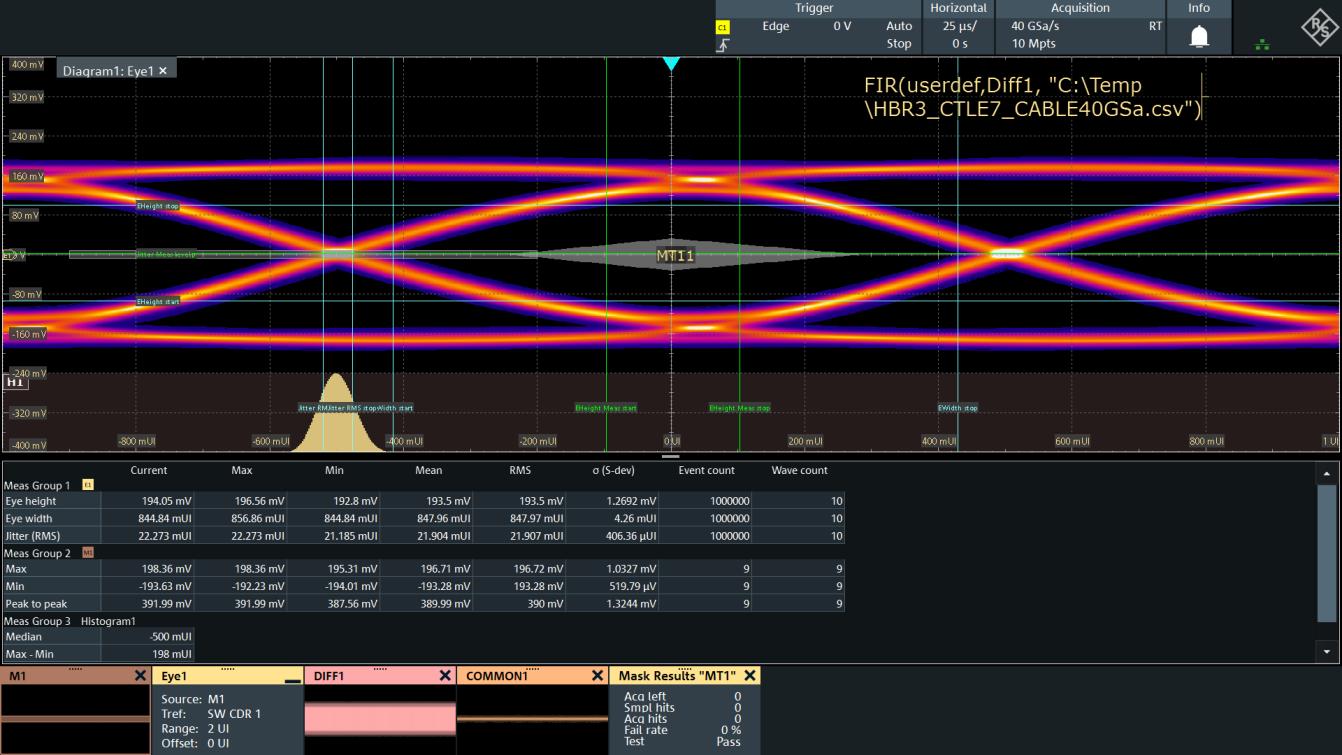

等化與眼圖分析

隨著傳輸速率提升(如 HBR2/HBR3),訊號經過線纜後會嚴重衰減,導致眼圖閉合,因此,CTS 規範了模擬接收端等化器的分析流程。

Figure 4: HBR3 傳輸速率下的各測試點眼圖

Table 1: 不同測試點的眼圖

測試點 |

描述 |

|

TP2 |

在訊號進入通道前,直接從發送端擷取的波形,此時眼圖張開度最大,幾乎沒有受到碼際干擾 (ISI) 的影響。 |

|

TP3_EQ |

將 TP2 的訊號透過一個「最差情況」的線纜模型進行數學運算後的結果,可以看到眼圖因插入損耗和色散而明顯劣化,反映了通道的全部影響。 |

|

TP3_CTLE |

在 TP3_EQ 的基礎上,再套用一個連續時間線性等化器 (CTLE) 的結果,它代表了訊號在一個標準接收機內被初步補償後的樣貌,是 HBR3 速率下進行眼圖規範性評估的標準。 |

測試軟體會自動掃描所有 CTLE 增益設置,找出能讓眼圖張開度最大的最佳配置 (TP3_CTLE_Optimal),若此時眼高仍不符合規範(例如 HBR3 要求 ≥65 mV),則可選擇性地啟用 DFE 來評估訊號的可恢復性。

Figure 5: 最佳化 CTLE 後的 TP3 眼圖 (TP3_CTLE_Optimal)

抖動分析

抖動分析專注於訊號時序的偏移,是驗證發送端穩定性的關鍵,測試會將抖動分解為隨機抖動 (RJ) 與確定性抖動 (DJ),有助於將時序問題追溯至具體的根源,例如雜訊、反射或時脈不穩定等。

Figure 6: 抖動分析結果

抖動分析同樣會在 TP2 與 TP3_CTLE 兩個測試點進行,對於 HBR3,TP3_CTLE 處的總抖動 (Total Jitter) 必須不大於 0.47 UI。

第二部分:線纜 (Cable) 測試

一個合規的發送端,若搭配一條劣質的線纜,整個鏈路的性能依然會功虧一簣,線纜會帶來插入損耗、回波損耗、阻抗不匹配等問題,因此對其進行完整的特性分析至關重要;線纜測試的核心工具是向量網路分析儀 (Vector Network Analyzer, VNA)。

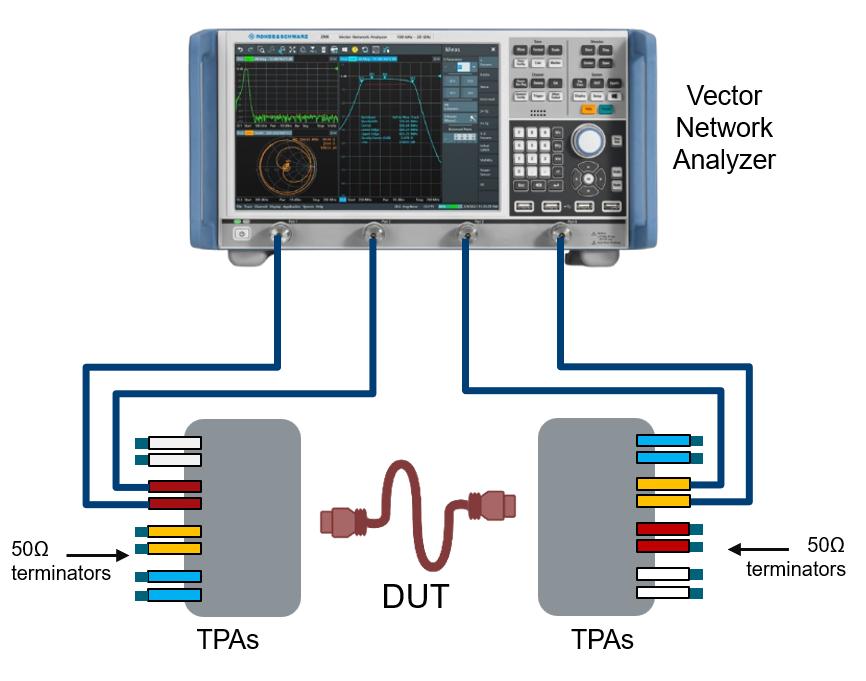

線纜分析測試設置

測試時,待測線纜會被連接在兩個 DisplayPort 插座治具之間,VNA 則透過同軸線纜連接到治具上,以進行四埠的差動 S 參數測量。

Figure 7: 線纜測試設置

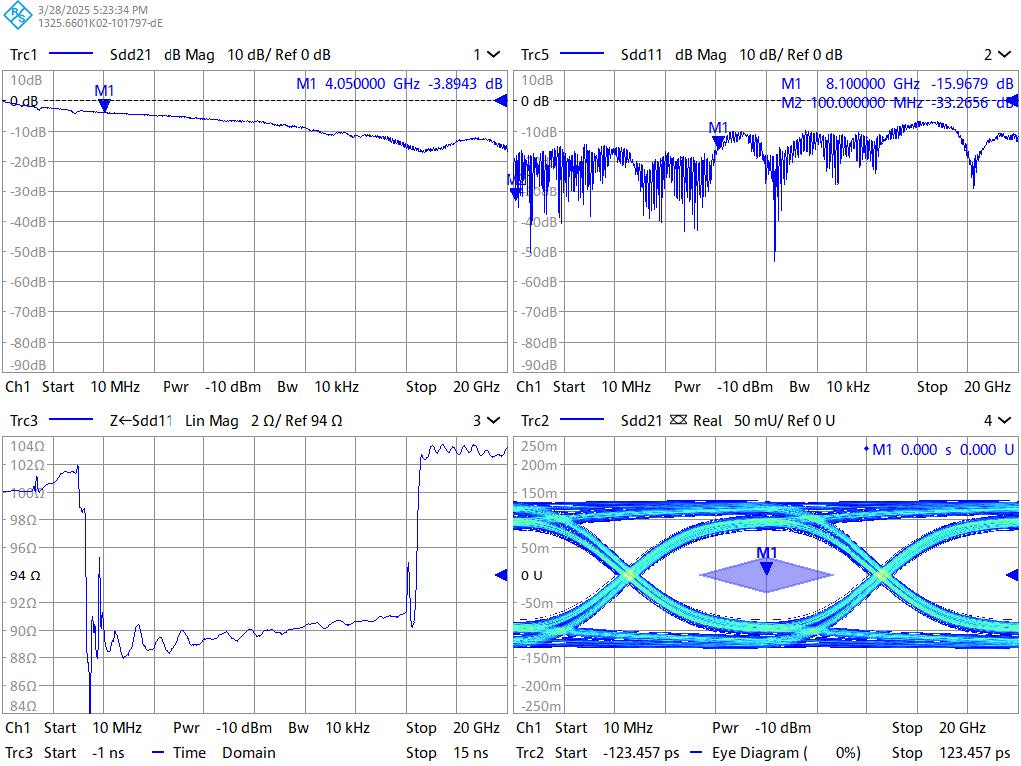

VNA 量測

經過精準的校準與治具去嵌入 (De-embedding) 後,VNA 可以量測出線纜的各項關鍵電氣特性。

Figure 8: VNA 量測結果

- SDD21 (差動插入損耗):描述訊號通過線纜後的衰減程度。

- SDD11 (差動回波損耗):反映線纜內部因阻抗不匹配造成的訊號反射量。

- TDR (時域反射儀):以時域方式呈現線纜沿線的阻抗變化,有助於定位瑕疵點。

- 模擬眼圖:基於量測到的 S 參數,數學運算出訊號通過此線纜後的模擬眼圖。

所有量測結果都需與 CTS 規範的遮罩 (Mask) 進行比對,以判定是否合規。

核心產品介紹

R&S®RTP 示波器

即時呈現訊號的完整性

R&S®RTP 高性能示波器結合了頂尖的訊號完整性與超快的擷取率,是進行 DisplayPort 發送端測試與除錯的理想平台,其高頻寬、即時解嵌功能與強大的分析軟體選項,確保了測試的精度與深度。

型錄下載 >

R&S®ZNB3000 向量網路分析儀

以超快量測週期實現最大產出

R&S®ZNB3000 VNA 具備極寬的動態範圍與超快的掃描速度,是通訊、航太國防應用的理想選擇,在 DisplayPort 線纜測試中,它能提供最精準、最可靠的 S 參數與 TDR 量測。

型錄下載 >

R&S®ZNXSIM VNA 模擬軟體

即使沒有硬體,VNA 也能隨時待命

此軟體能讓 VNA 的所有功能在 PC 上運行,工程師可以在沒有實體儀器的情況下,預先設定測試、分析量測數據,或開發自動化程式,大幅提升工作效率。

配置指南

發送端測試所需儀器與配件

|

儀器/配件 |

類別 |

數量 |

訂購編號 |

描述 |

|

R&S®RTP 134B / RTP 164B |

示波器 |

1 |

1803.7000.13 / 1803.7000.16 |

頻寬最高達 16 GHz |

|

R&S®RT-ZA17 |

探棒配件 |

1 |

1377.8991.02 |

匹配電纜對 |

|

R&S®RT-ZS10 |

主動式探棒 |

2 |

1410.4080.02 |

AUX 通道測試 |

|

R&S®RTP-K114 |

軟體 |

1 |

1803.6903.02 |

DP 1.4a 一致性測試選項 |

|

R&S®RTP-K115 |

軟體 |

1 |

1803.6910.02 |

eDP 1.4b/1.5 一致性測試選項 |

|

R&S®RTP-K137 |

軟體 |

1 |

1800.6983.02 |

進階眼圖分析 |

|

R&S®RTP-K141 |

軟體套組 |

1 |

1326.4560.02 |

16 Gbps 序列碼型觸發 |

|

R&S®RTP-K133 |

軟體 (可選) |

1 |

1800.6860.02 |

抖動與雜訊分解 |

|

R&S®RTP-K126 |

軟體 |

1 |

1800.6025.02 |

嵌入與等化 (手動濾波器調整) |

線纜測試所需儀器與配件

|

儀器/配件 |

類別 |

數量 |

訂購編號 |

描述 |

|

R&S®ZNB3020 |

VNA |

1 |

1351.5050.24 |

頻寬:20 GHz |

|

R&S®ZV-Z193 |

RF 線纜 |

4 |

1306.4565.06 |

頻率範圍:18 GHz – 110 GHz |

|

R&S®ZN-Z52 |

校準套件 |

1 |

1335.6991.30 |

4 埠校準單元, 100 kHz – 26.5 GHz |

|

R&S®ZNXSIM |

模擬環境 |

1 |

1325.6601.02 |

VNA 模擬環境 |